ECE320L

# Theory of Digital Systems Laboratory Manual

California State University, Northridge

Prepared by: Soraya Roosta

## Table of Contents

|                                                        |     |

|--------------------------------------------------------|-----|

| Acknowledgment .....                                   | 3   |

| Introduction .....                                     | 4   |

| Introduction to PSPICE and Logic Gate Simulation ..... | 5   |

| Circuit Introduction with LEDs.....                    | 28  |

| Logic Gates and Pull-Up and Pull-Down Resistors .....  | 35  |

| Boolean Laws And DeMorgan's Theorems.....              | 42  |

| Logic Circuit Simplification .....                     | 54  |

| Half / Full Adder PSPICE Simulation .....              | 61  |

| 2's Complement Adder / Subtractor Circuit .....        | 78  |

| Multiplexers .....                                     | 82  |

| Demultiplexer .....                                    | 91  |

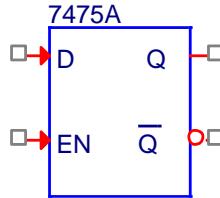

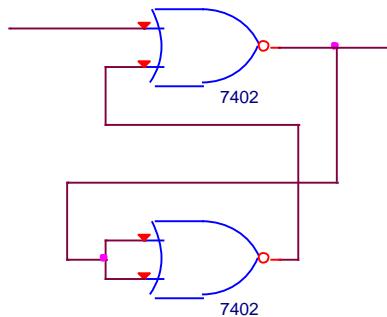

| D Latch and D Flip-Flop .....                          | 97  |

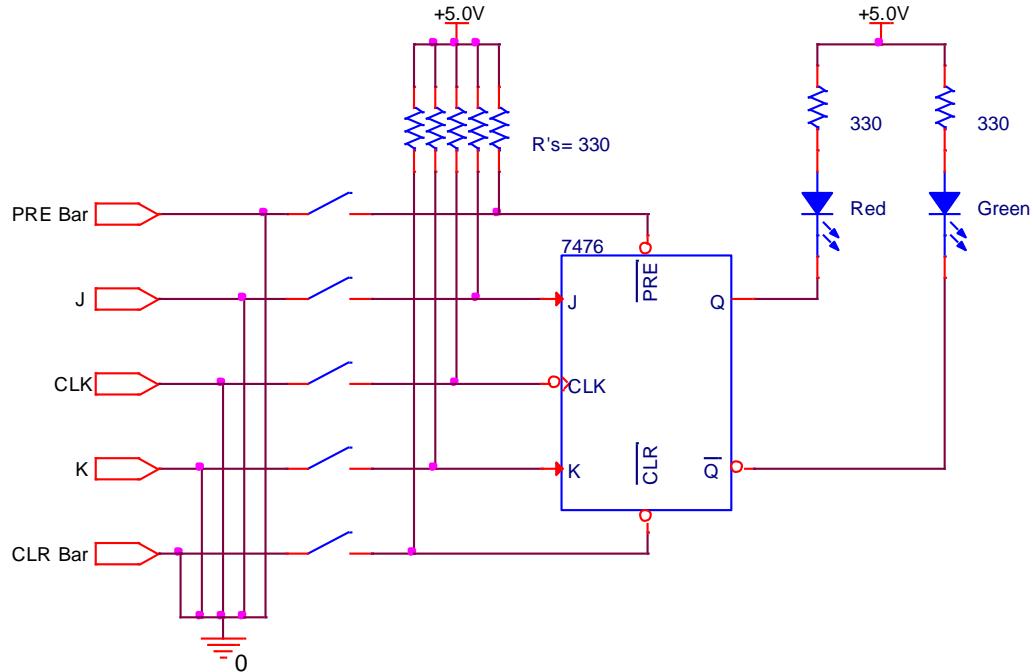

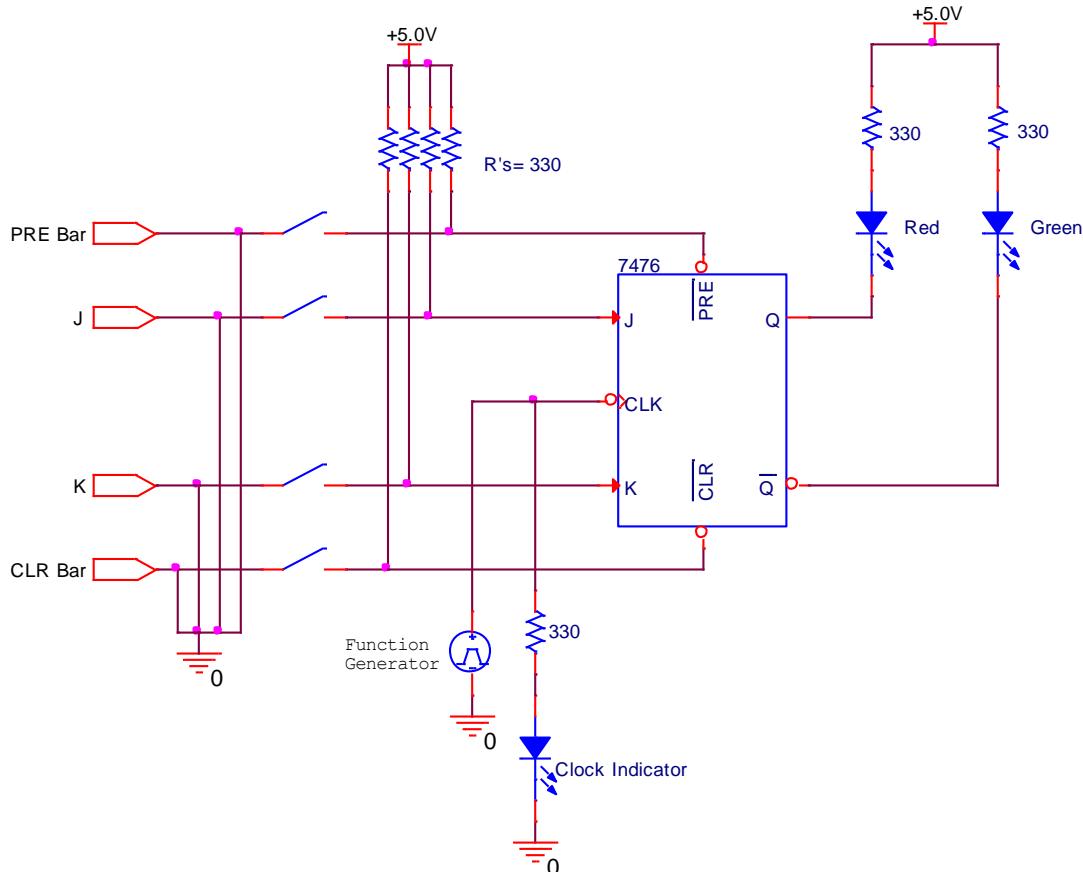

| J-K Flip-Flop .....                                    | 107 |

| Asynchronous Counter.....                              | 114 |

| Analysis of Synchronous Counters with Decoding .....   | 125 |

| Design of Synchronous Counters .....                   | 133 |

## Acknowledgment

I would like to thank Dr. George Law for providing his OrCAD based experiments. I would also like to thank Dr. Ramin Roosta for reviewing the manual and his suggestions.

Special thanks to my T.A., Michael Granberry, for setting up the OrCAD for the experiments and for his help in modifying the experiments.

I would also like to acknowledge the support and encouragement of Dr. Ashley Geng.

## Introduction

### HELLO STUDENTS

Welcome to the digital logic lab! In this lab, you will have the opportunity to experiment with and learn about digital logic circuits. You will use a variety of equipment, such as power supplies, digital multimeters, function generators, and oscilloscopes as well as software tools for simulating and modeling digital circuits.

The focus of this lab is to provide hands-on experience for students studying digital electronics and computer engineering, allowing you to apply the theoretical concepts you have learned in class to real-world situations. You will learn how to design, build, and test digital circuits using a variety of logic gates and other digital building blocks.

Throughout the lab, you will work on a series of exercises and projects designed to help you understand the fundamental principles of digital logic. These exercises will include basic logic gates, such as AND, OR, and NOT, as well as more complex circuits like flip-flops and counters.

This lab will require a lot of time, effort, and attention to details, so be prepared by reviewing the materials before coming to class. You will be working with equipment that can be fragile and expensive, so please handle it with care.

You will also be required to keep a lab notebook (paper or electronic), where you will record your observations and measurements, and to present the results of your work. Also, you will be required to turn in lab reports each week. Let's get started and have a great time learning about digital logic!

# Introduction to PSPICE and Logic Gate Simulation

## OBJECTIVES

---

After completing this experiment, you will be able to

- Simulated the 7 fundamental logic gates on OrCAD PSPICE.

## MATERIALS NEEDED

---

- OrCAD PSPICE

## THEORY

---

### ORCAD PSPICE:

In this experiment, we will simulate all 7 fundamental logic gates to gain familiarity with OrCAD PSPICE. OrCAD PSpice is a software tool for simulating and analyzing the behavior of electronic circuits. It is a component of the OrCAD electronic design automation (EDA) suite, which is used to design and manufacture electronic systems and components.

PSpice provides a wide range of simulation models and analysis tools for analog, digital, and mixed-signal circuits. It allows designers to analyze the performance of their circuits under different operating conditions and identify potential issues before physically building and testing the circuits. The software has a graphical user interface (GUI) that allows users to build and edit circuits using schematic capture and layout tools. It also includes a variety of libraries of pre-defined components, such as transistors, resistors, capacitors, and integrated circuits, that can be added to circuits.

PSpice is widely used in the electronics industry and academia for designing and testing electronic circuits, including power supplies, amplifiers, filters, and controllers.

### 7 FUNDAMENTAL LOGIC GATES:

Digital logic gates are electronic circuits that perform logical operations on one or more input signals and produce an output signal based on the logical operation. They are the basic building blocks of digital circuits and are used to implement Boolean functions, which are mathematical functions that take in one or more input values and produce a single output value.

There are several types of digital logic gates, including:

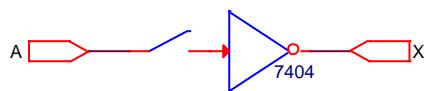

### INVERTER

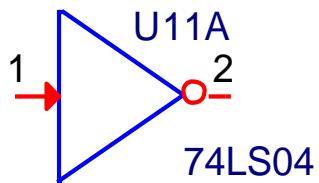

Figure 1. 1

| Input | Output |

|-------|--------|

| X     | Y      |

| 1     | 0      |

| 0     | 1      |

Table 1. 1

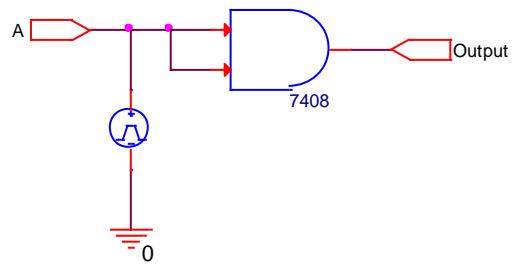

### AND

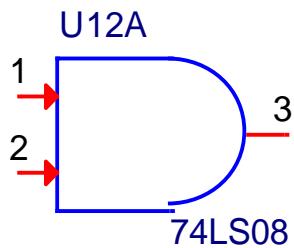

Figure 1. 2

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 0      |

| 0 1   | 0      |

| 1 0   | 0      |

| 1 1   | 1      |

Table 1. 2

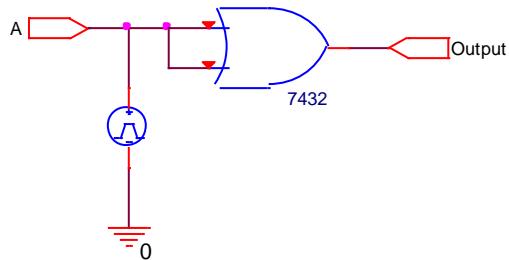

### OR

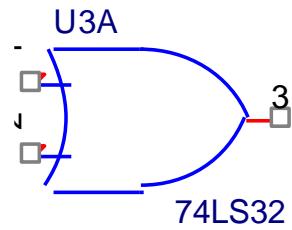

Figure 1. 3

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 0      |

| 0 1   | 1      |

| 1 0   | 1      |

| 1 1   | 1      |

Table 1. 3

### NAND

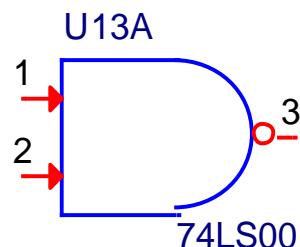

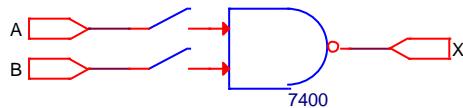

Figure 1. 4

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 1      |

| 0 1   | 1      |

| 1 0   | 1      |

| 1 1   | 0      |

Table 1. 4

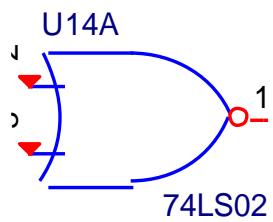

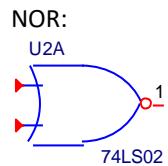

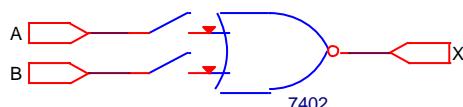

### NOR

Figure 1. 5

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 1      |

| 0 1   | 0      |

| 1 0   | 0      |

| 1 1   | 0      |

Table 1. 5

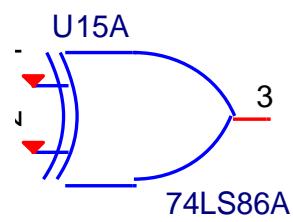

### XOR

Figure 1. 6

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 0      |

| 0 1   | 1      |

| 1 0   | 1      |

| 1 1   | 0      |

Table 1. 6

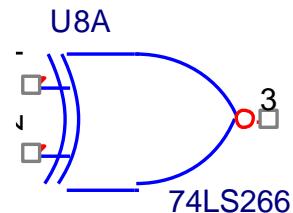

### XNOR

Figure 1. 7

| Input | Output |

|-------|--------|

| A B   | Y      |

| 0 0   | 1      |

| 0 1   | 0      |

| 1 0   | 0      |

| 1 1   | 1      |

Table 1. 7

## PRELIMINARY PROCEDURE

1. Read the lab.

2. Draw the output waveform for each logic gate. We will use these results to compare with your PSPICE simulations.

|      |                                                                                      |

|------|--------------------------------------------------------------------------------------|

| X    |    |

| Y    |    |

| NOT  |    |

| AND  |    |

| OR   |    |

| XOR  |    |

| NAND |   |

| NOR  |  |

| XNOR |  |

Table 1. 8

## PROCEDURE

---

### SIMULATING A NOT GATE IN PSPICE

#### STARTING A NEW PROJECT

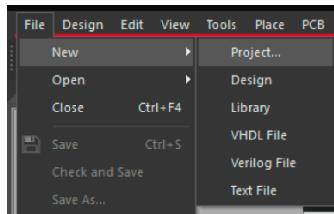

1. Press File > New > Project to begin a new project.

Figure 1. 8

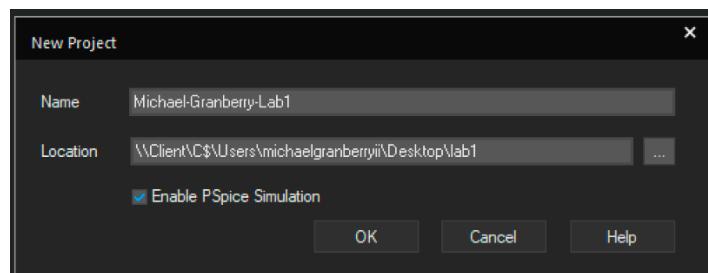

2. In the New Project window, title your file "FirstName-LastName-Lab1", for example. Save it in a folder called "Lab 1". Check the box called Enable PSpice Simulation.

Figure 1. 9

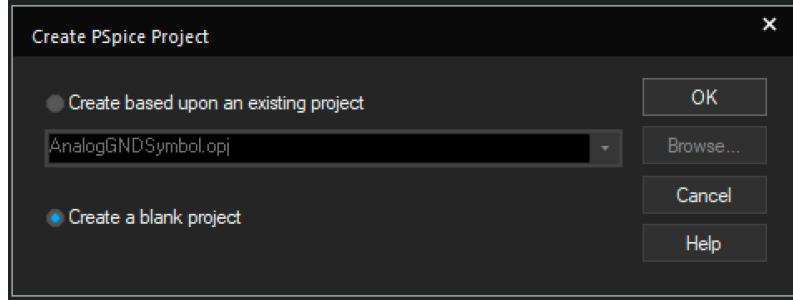

3. In the Create PSpice Project pop-up window, select **Create a blank project** and Press **OK**.

Figure 1. 10

#### ADDING LIBRARIES

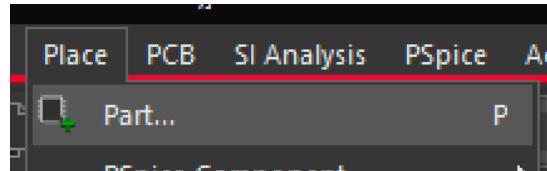

4. Press **Place > Part** or press **P** to bring up the parts library.

Figure 1. 11

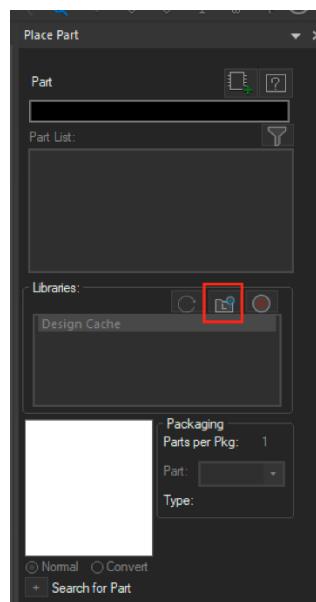

5. In Place Part window, click the Add Library icon,  In the **Design Cache** folder, open the library called 74LS, SOURCSTM.

Figure 1. 12

#### ADDING COMPONENTS TO SCHEMATIC

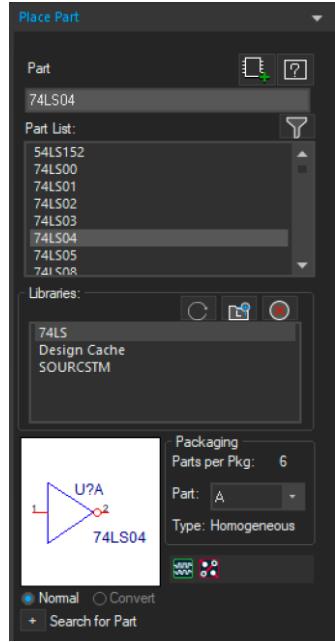

6. Now that your libraries are imported, select 74LS in the library window and search for 74LS04 by typing it in the search window and press **ENTER/RETURN** on your keyboard.

Figure 1. 13

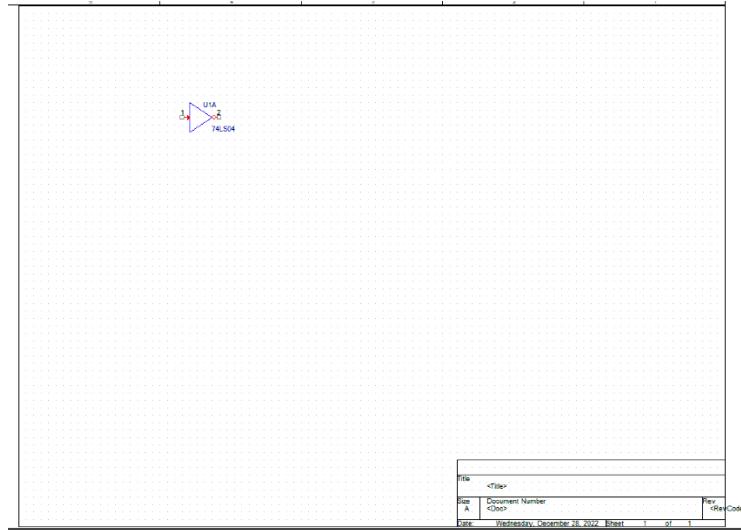

7. Drag your mouse over your schematic window and place the NOT gate on your schematic.

Figure 1. 14

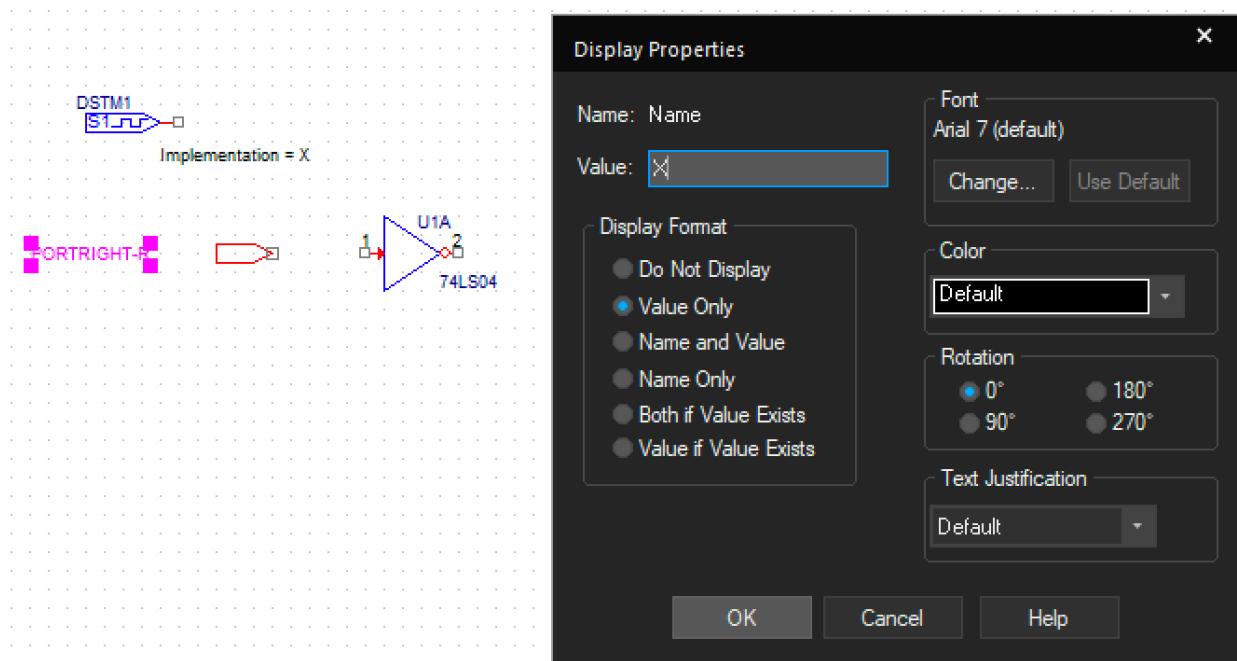

8. In the SOURCSTM library, search for DigStim1 and add one to your schematic. Double click “Implementation” text and type “X” in the Value textbox with Display Format set to Name and Value. Press **OK**.

Figure 1. 15

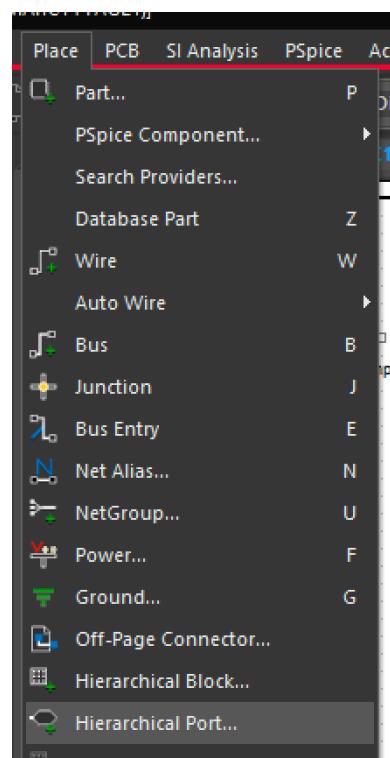

9. Add ports by going to Place > Hierarchical Port....

Figure 1. 16

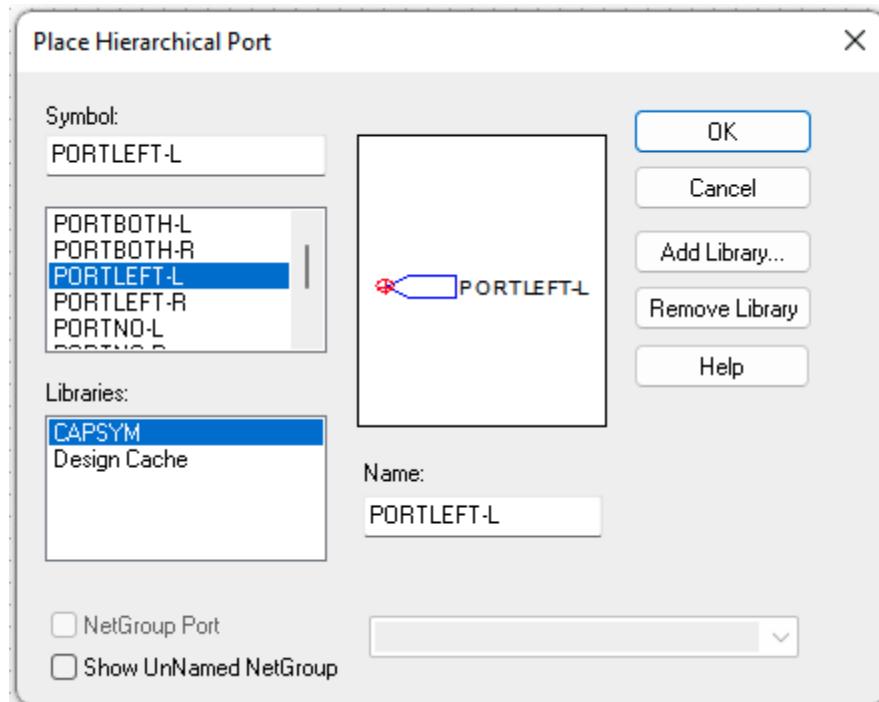

10. Search for PORTLEFT-R in the CAPSYM library. Press **OK**. Place at the input of the NOT gate.

Figure 1. 17

11. Double click on the “PORTLEFT-R” text and rename it “X”.

Figure 1. 18

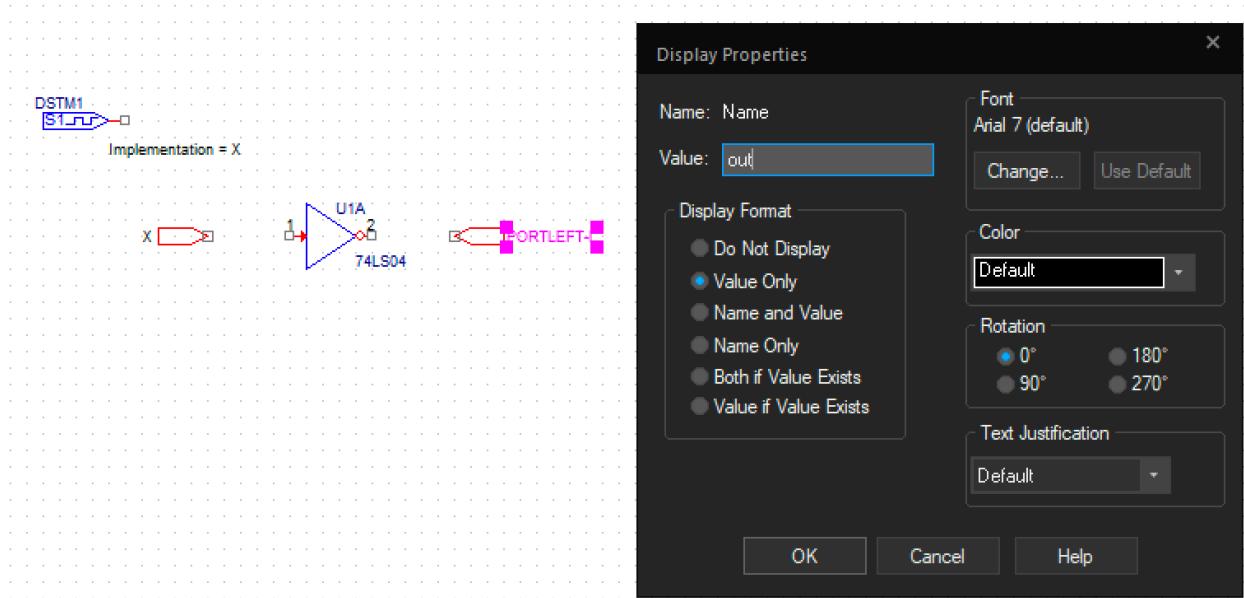

12. Similar for the output, place a PORTLEFT-L at the output of the NOT gate and rename it “out”.

Figure 1. 19

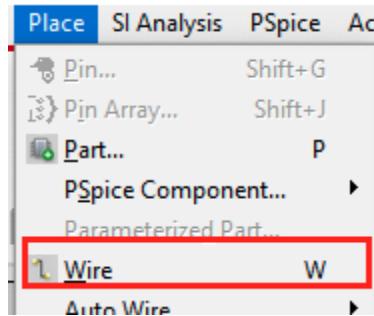

13. To connect the components together on the schematic with wires, go to **Place > Wire** or press **W**.

Figure 1. 20

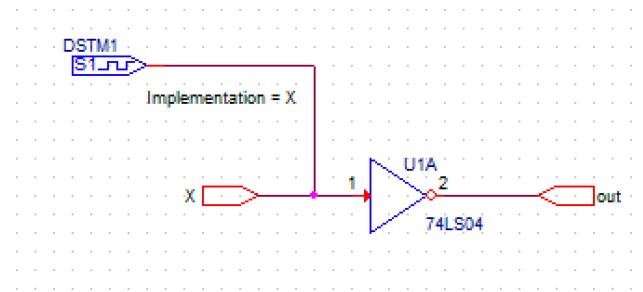

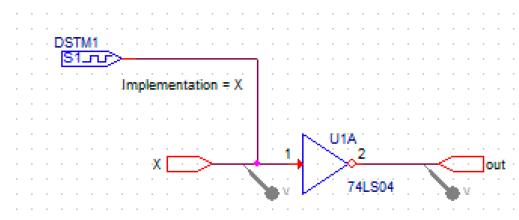

14. Connect the components together in a similar manner as shown below.

Figure 1. 21

## CREATING A NEW SIMULATION PROFILE

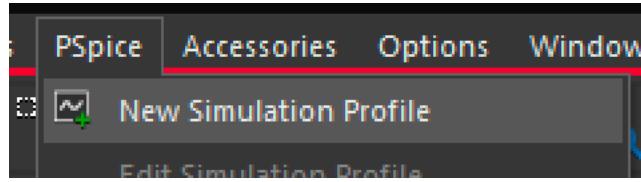

15. Create a new simulation profile by pressing **PSpice > New Simulation Profile** or click the  icon.

Figure 1. 22

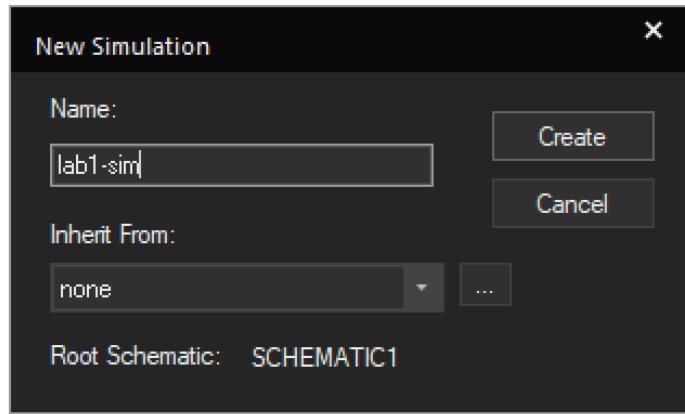

16. In the pop-up window type “lab1-sim”. Press Create when done. Leave Inherit From as none.

Figure 1. 23

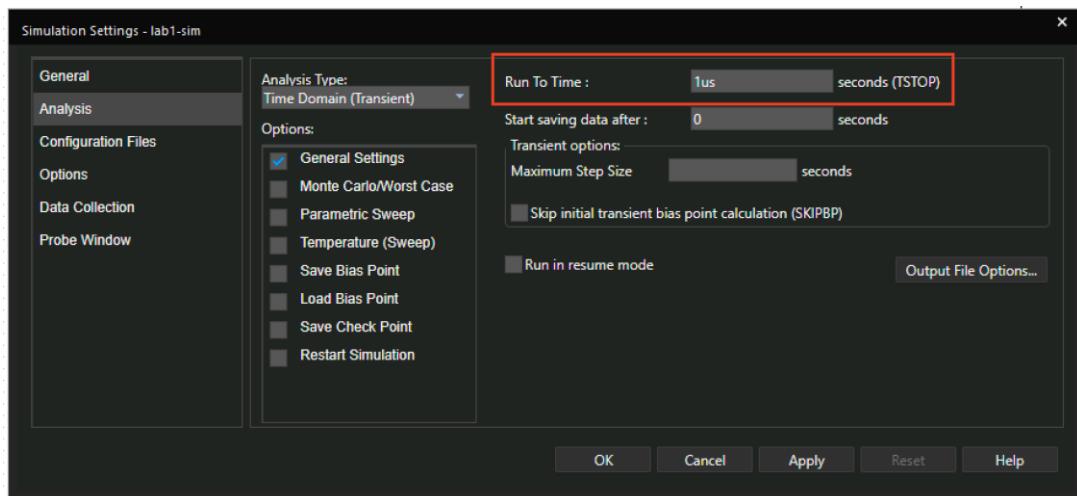

17. A window called “Simulation Settings – lab1-sim” will pop-up. Set Run To Time to “1us”. This will make the simulation run for 1us.

Figure 1. 24

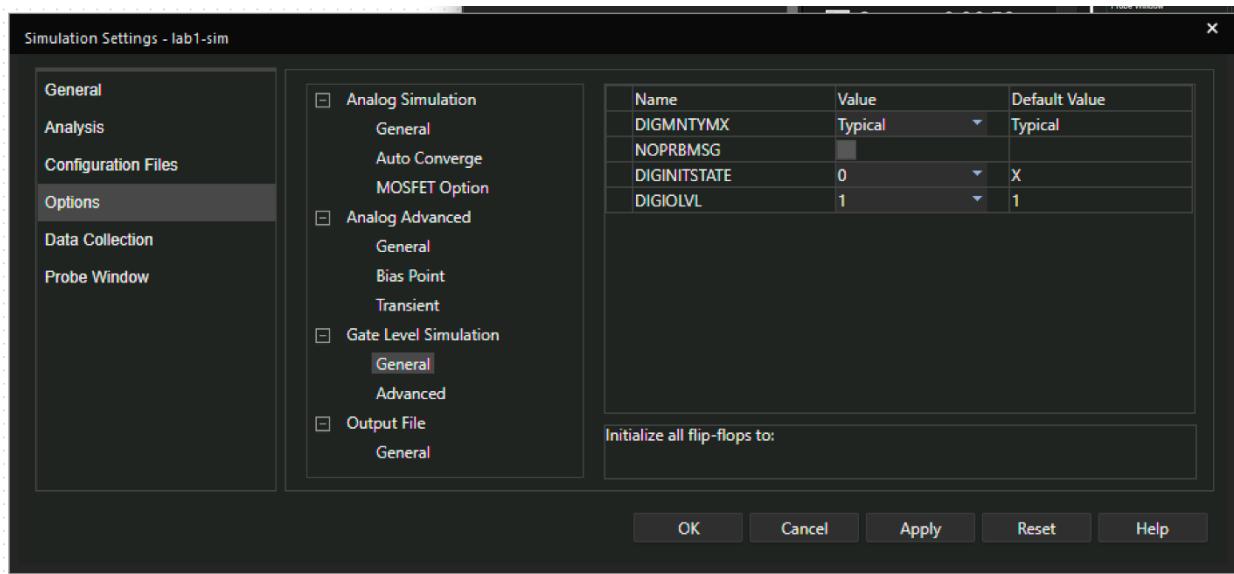

18. Next, click on **Options > Gate Level Simulation > General** and set DIGINITSTATE to 0 under the Value column. Then press **Apply**, then **OK**.

Figure 1. 25

#### CREATING A SIMULATION STIMULI

OrCAD Capture Lite offers several ways to create simulation stimuli. One way is to do it manually and another way is to treat the inputs as if they are clocks. We will look at both methods this lab.

##### CREATE MANUALLY

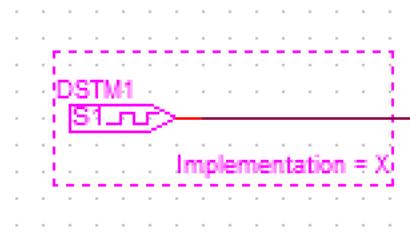

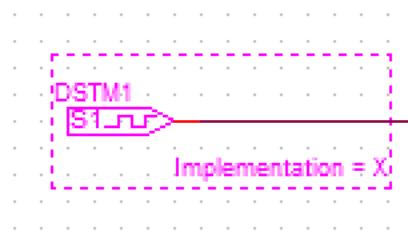

19. Click the DSTM1 symbol to select the part so that a purple dotted rectangle encloses the part.

Figure 1. 26

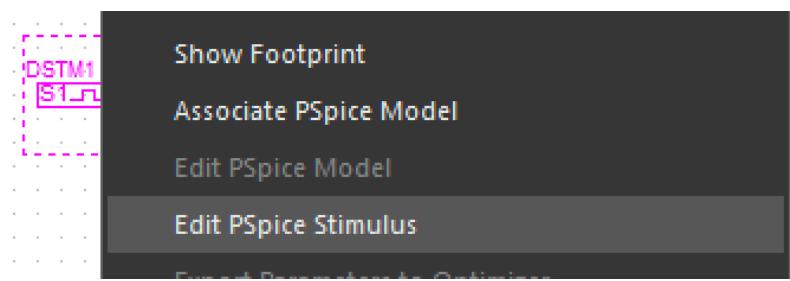

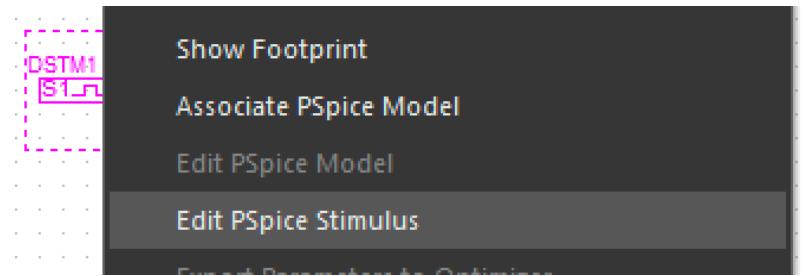

20. Right click on the DSTM1 symbol and click Edit PSpice Stimulus.

Figure 1. 27

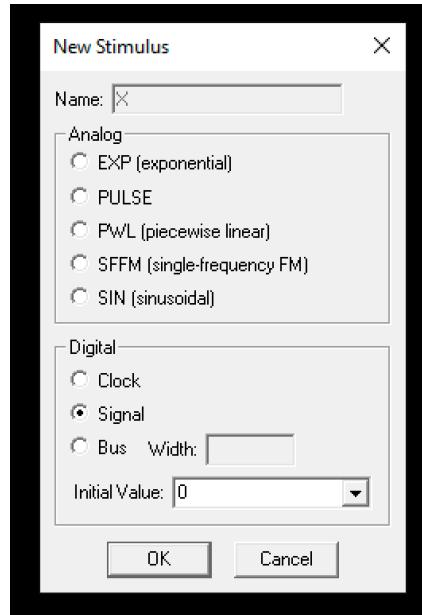

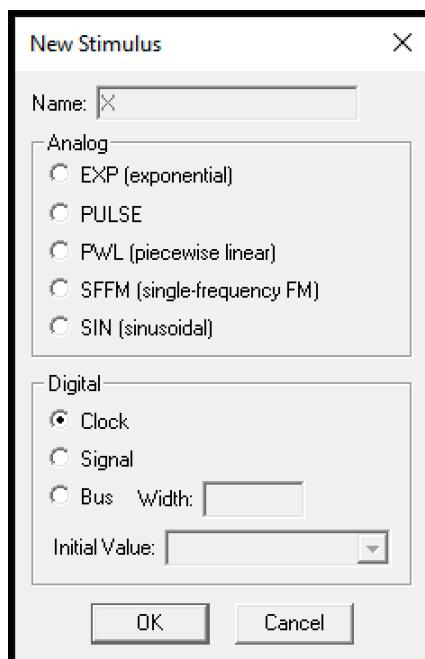

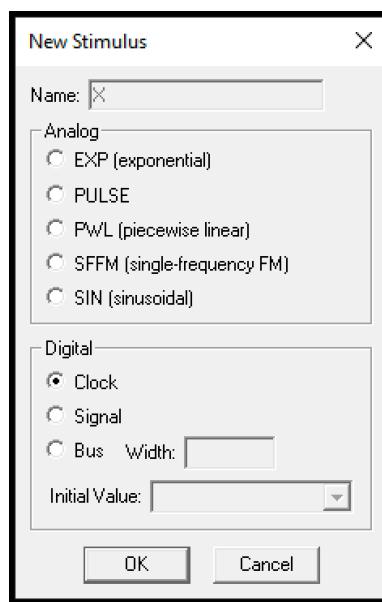

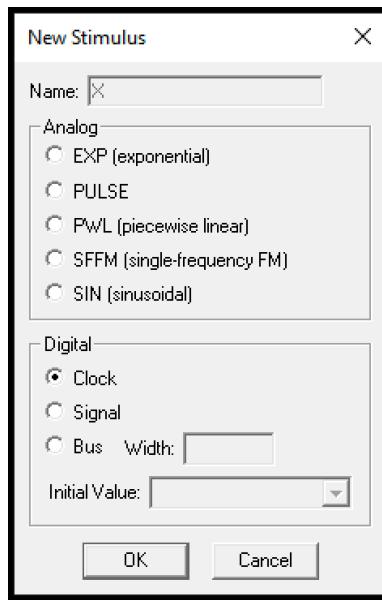

21. A New Stimulus window will pop up with "X" already in the Name text field. In the Digital section, select Signal,

then press **OK**.

Figure 1. 28

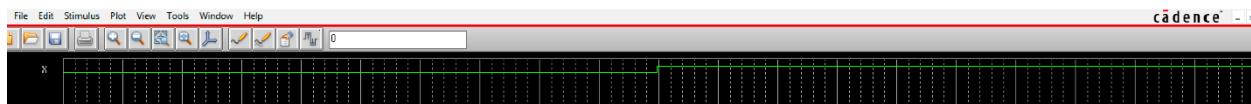

22. To add a new point or a transition to a stimulus, click the  icon. Now, the arrow cursor symbol has become a pencil symbol. Use this tool to toggle your input signal between 0 and 1. That is, once you have this tool selected, click on the green signal to change the logic level. Toggle your signal from 0 to 1 at 0.5us. Your final signals should look like the following.

Figure 1. 29

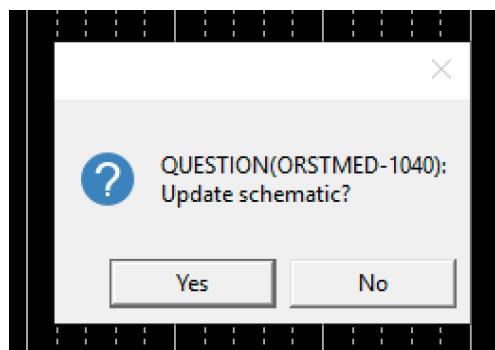

23. Press **Save** and press **Yes** to update schematic.

Figure 1. 30

**RUN SIMULATION**

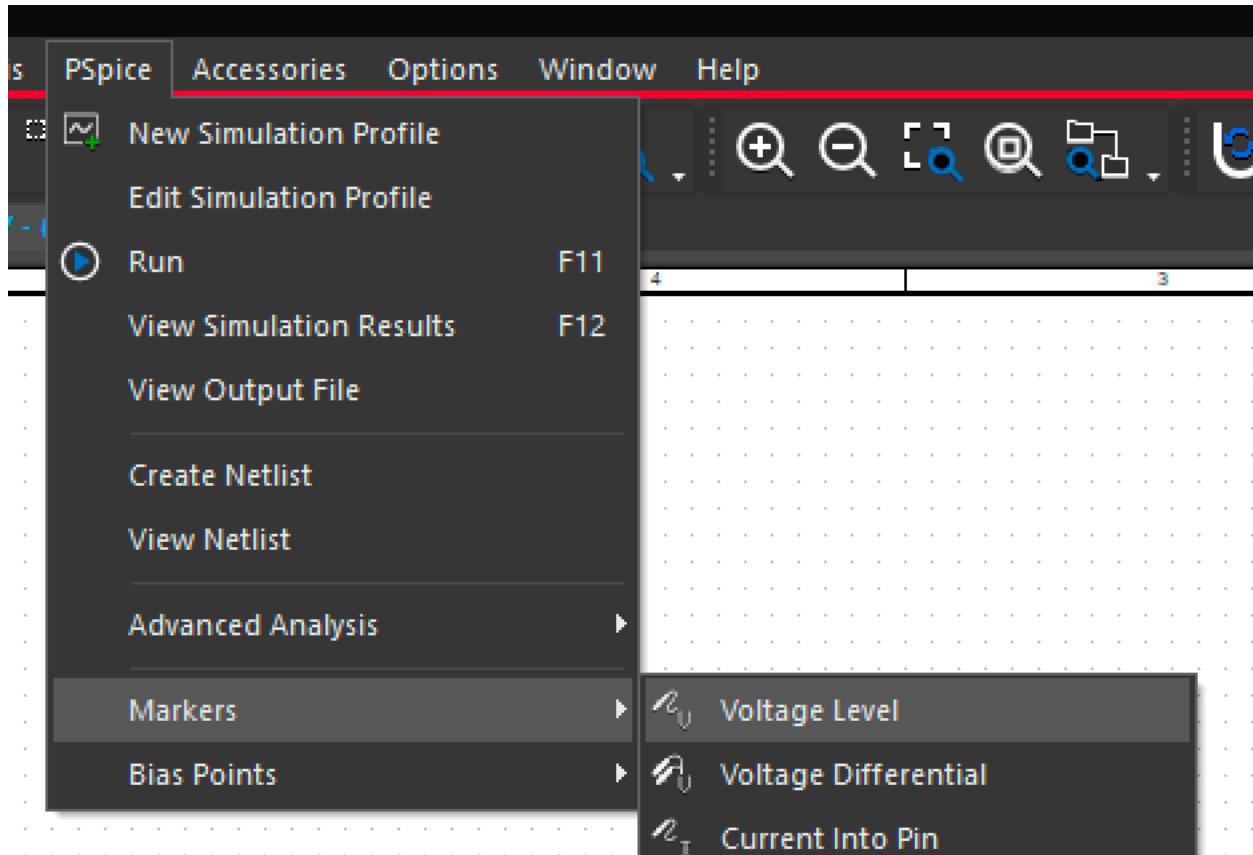

24. Place *Voltage Level* markers schematic by going to **PSPICE > Markers > Voltage Level** or press  icon.

Figure 1. 31

25. The Voltage Level markers must be placed on the wires.

Figure 1. 32

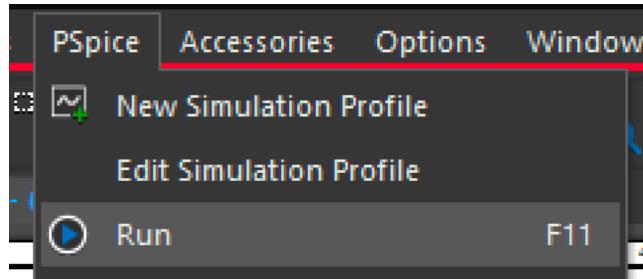

26. Press PSpice > Run or the  icon to run simulation.

Figure 1. 33

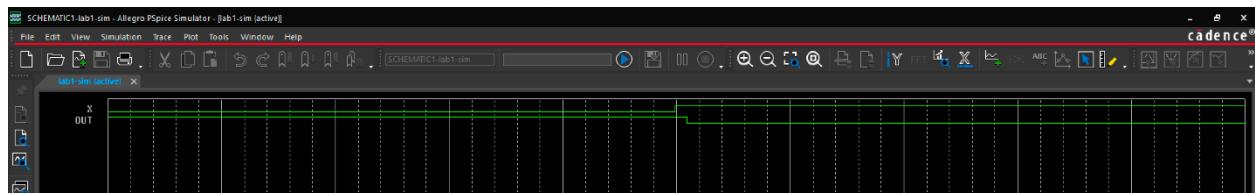

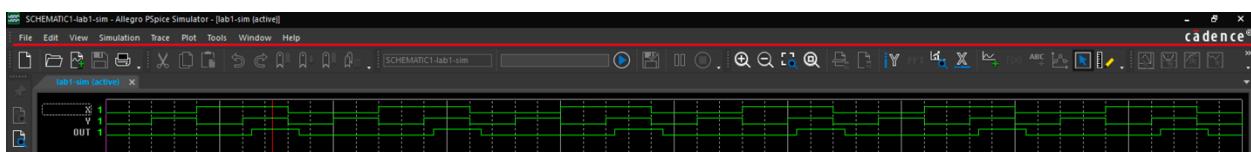

27. Running the simulation will cause the Allegro PSpice Simulator program to open which will contain a simulation of your schematic. It should look like the screenshot below.

Figure 1. 34

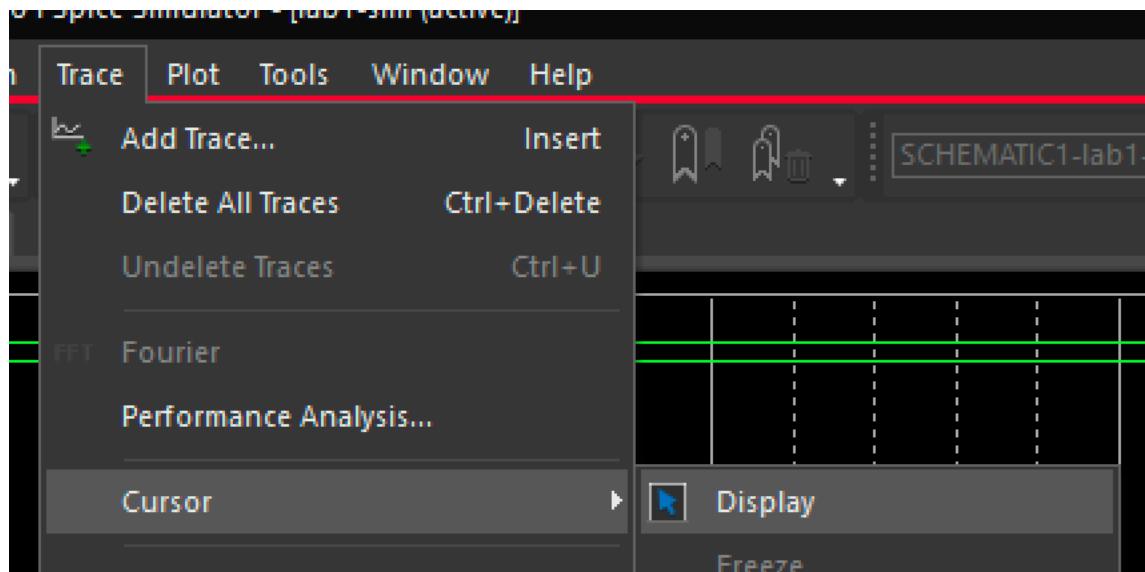

28. Press **Trace > Cursor > Display** or press to enable the cursor.

Figure 1. 35

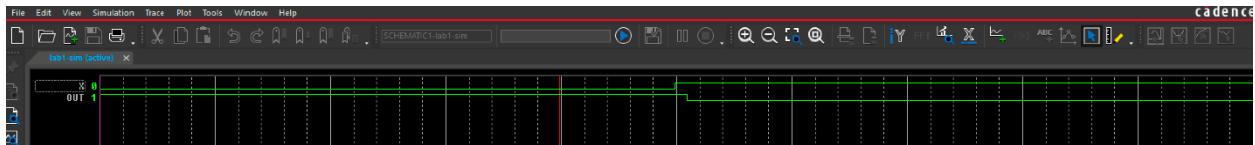

29. This will let you see the level of your signal. Once enabled, left click and on your simulation to see the levels of your signal. You can click hold and drag as well.

Figure 1.36

30. Compare your simulated results with your pre-lab.

## SIMULATING AN AND GATE IN PSPICE

The implementation and simulation for an AND gate is very similar to the NOT gate demonstrated previously.

### STARTING A NEW PROJECT

1. Create a new project by going to **File > New > New Project....**

2. In the New Project window, name your project and save it in a new folder.

3. In the Create PSPICE Project window, click **Create a black project**, then press **OK**.

### ADDING LIBRARIES

4. The necessary libraries should already be added to your library list from implementing the NOT gate. If not, refer to step 2 in the from the previous section.

### ADDING COMPONENTS TO SCHEMATIC

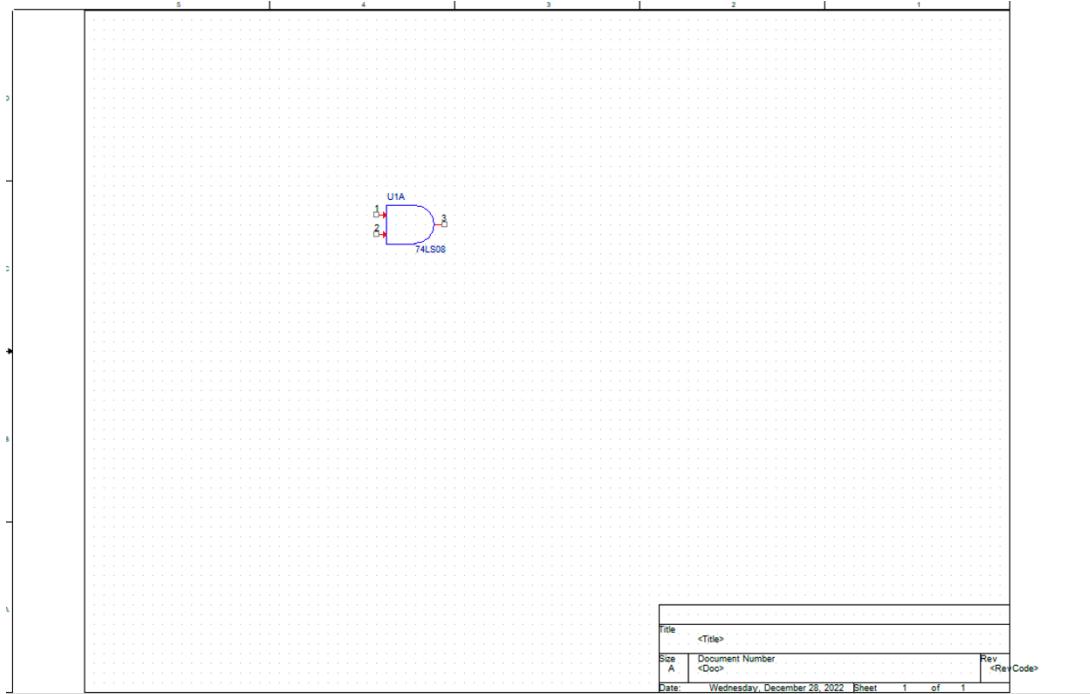

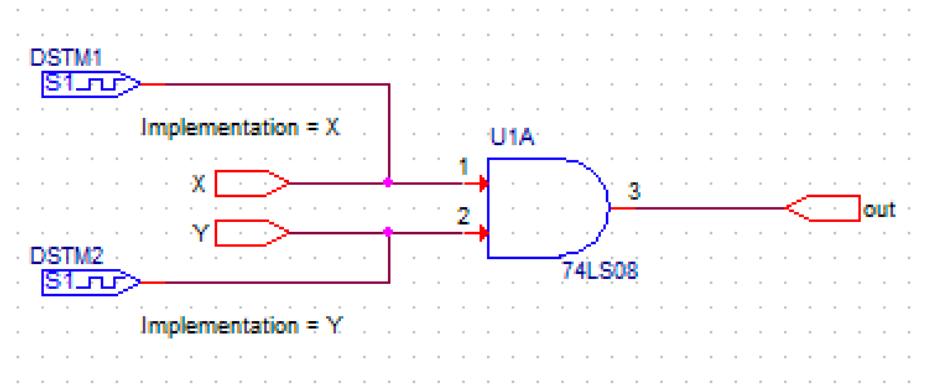

5. Open your parts window by pressing **P** and search for 74LS08 in the 74LS library. The 74LS08 is an AND gate. Place the AND gate on your schematic. So far you should have the following:

Figure 1.37

6. Place two DigStim1 parts on your schematic (one for each input). Double click on the “Implementation” text and set the value to X and Y for each DigStim1.

7. Go to **Place > Hierarchical Port...** and place two PORTRIGHT-R ports to the left of the inputs of the AND gate.

Double click on the “PORTRIGHT-R” text and rename each port X and Y for each port.

8. Similarly, go to **Place > Hierarchical Port...** and place one PORTRIGHT-L port to the right of the output of the AND gate. Double click on the “PORTLEFT-L” text and rename it out.

9. Press **W** for the wire tool and connect each component together with wires. So far you should have the following:

Figure 1. 38

#### CREATING A NEW SIMULATION PROFILE

10. Create a new simulation profile by pressing **PSpice > New Simulation Profile** or click the  icon.

11. In the pop-up window type “lab1-sim”. Press Create when done. Leave Inherit From as none.

12. A window called “Simulation Settings – lab1-sim” will pop-up. Set Run To Time to “1us”. This will make the simulation run for 1us.

13. Next, click on **Options > Gate Level Simulation > General** and set DIGINITSTATE to 0 under the Value column. Then press **Apply**, then **OK**.

#### CREATING A SIMULATION STIMULI

Now we will look at the second way to create simulation stimuli by treating the inputs as if they are clocks.

#### TREAT SIGNALS AS CLOCKS

14. Click the DSTM1 symbol to select the part so that a purple dotted rectangle encloses the part.

Figure 1. 39

15. Right click on the DSTM1 symbol and click **Edit PSpice Stimulus** from the menu.

Figure 1. 40

16. A New Stimulus window will pop up with “X” already in the Name text field. In the Digital section, select Signal, then press **OK**.

Figure 1. 41

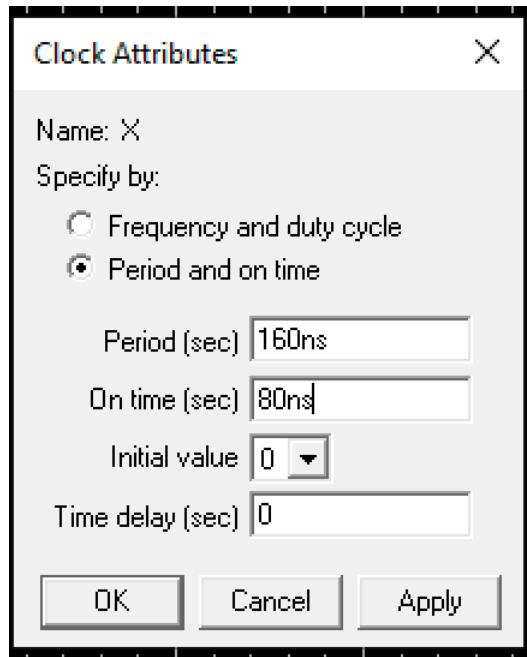

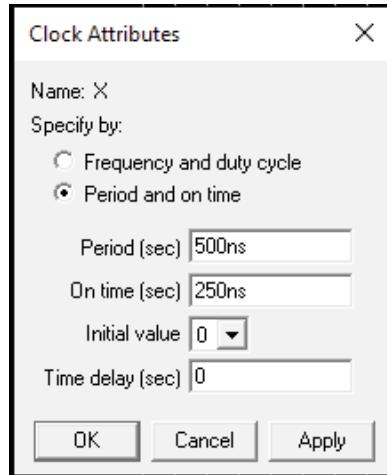

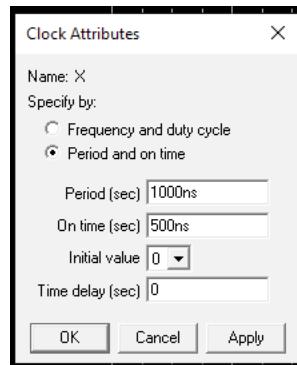

17. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 160ns and On time (sec) to 80ns. Press **Apply**, then **OK**.

Figure 1. 42

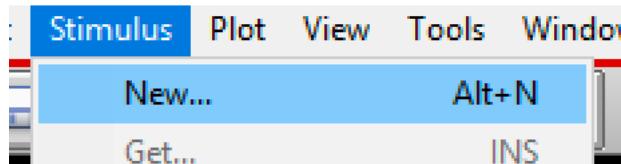

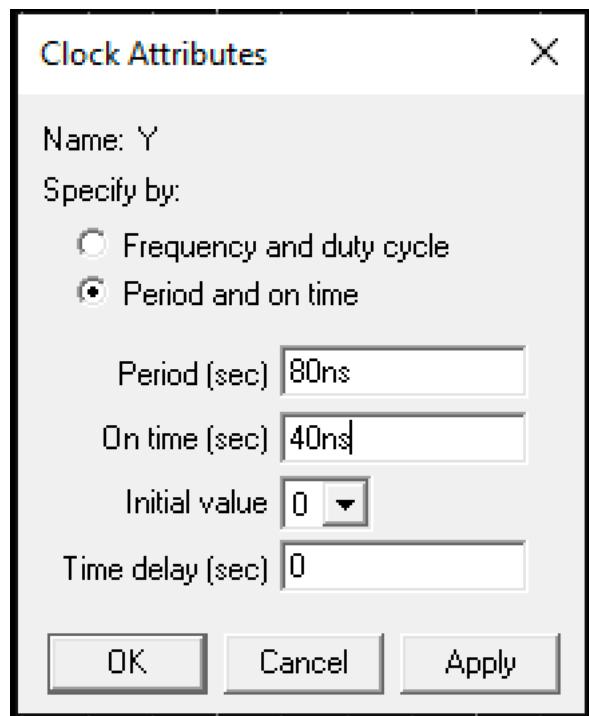

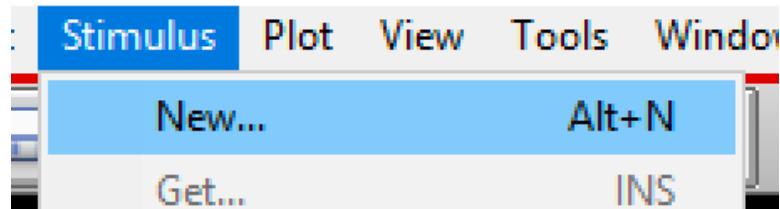

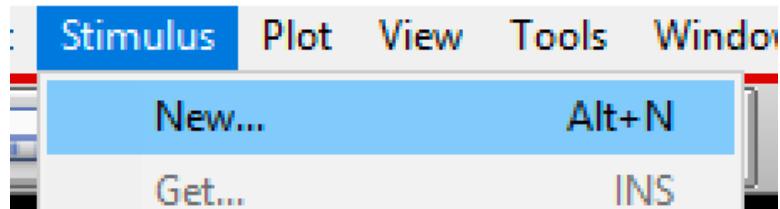

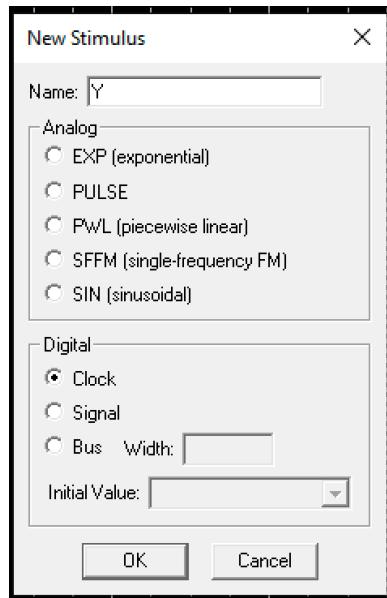

18. Set another stimulus for Y, press **Stimulus > New...**

Figure 1. 43

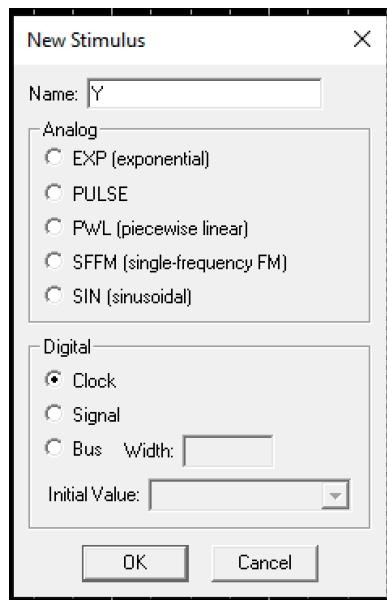

Figure 1. 44

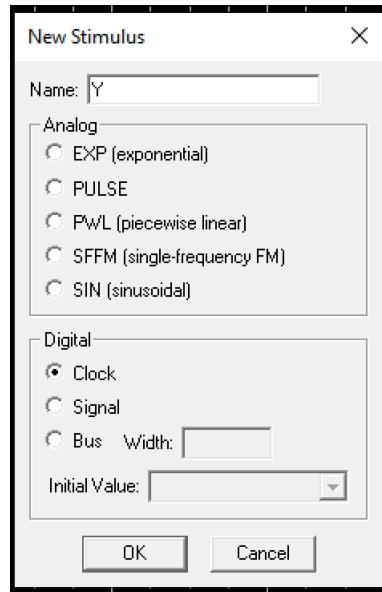

19. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 80ns and On time (sec) to 40ns. Press **Apply**, then **OK**.

Figure 1. 45

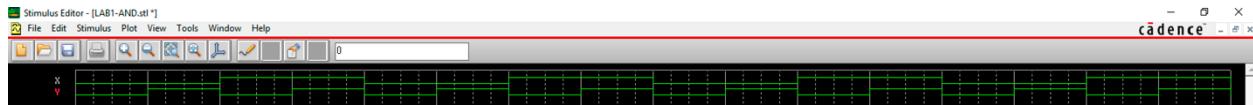

20. Your Stimulus Editor should look like the following:

Figure 1. 46

21. Press **Save** and press **Yes** to update schematic.

Figure 1. 47

## RUN SIMULATION

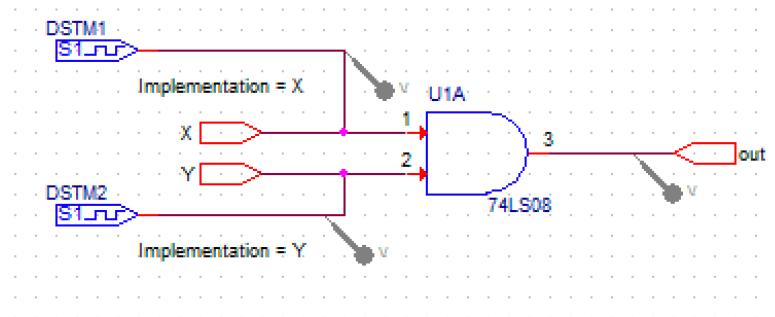

22. Place Voltage Level markers schematic by going to **PSpice > Markers > Voltage Level** or press the  icon. The Voltage Level markers must be placed on the wires. Your schematic should look like the following:

Figure 1. 48

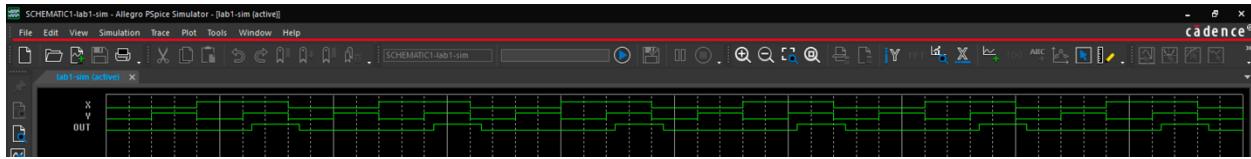

23. Press **PSpice > Run** or the  icon to run simulation. Running the simulation will cause the Allegro PSpice Simulator program to open which will contain a simulation of your schematic. It should look similar to the screenshot below:

Figure 1.49

24. Press **Trace > Cursor > Display** or press  to enable the cursor. This will let you see the level of your signal. Once enabled, left click and on your simulation to see the levels of your signal. You can click hold and drag as well.

Figure 1.50

25. Compare your simulated results with your pre-lab.

## PRACTICE PSPICE

Here you will practice the steps above and simulate the remaining gates on your own.

Parts List in the 74LS library:

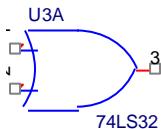

OR: 74LS32

Figure 1.51

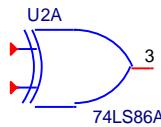

XOR: 74LS86A

Figure 1.52

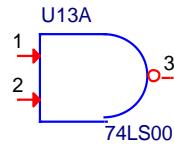

NAND:

Figure 1.53

Figure 1. 54

XNOR:

When you simulate the 74LS266, a '1' will be simulated as a 'Z' (high impedance).

Figure 1. 55

For the remaining logic gates, compare your simulated results with your pre-lab.

## Circuit Introduction with LEDs

### OBJECTIVES

After completing this experiment, you will be able to:

- Use a DC power supply and DMM.

- Identify basic circuit components.

- Analyze a circuit containing a switch.

- Analyze a simple LED circuit and measure the forward voltage.

### MATERIALS NEEDED

- One  $330\Omega$

- Red, orange, yellow, green, blue, white LEDs

- 7404 hex inverter IC

### THEORY

#### DIGITAL MULTIMETER (DMM)

A DMM, or Digital Multimeter, is a versatile electronic device used to measure various electrical quantities in a simple and convenient way. A DMM typically has a digital display that shows numerical readings for measurements such as voltage, current, resistance, and sometimes frequency.

#### GROUND

In a circuit, "ground" refers to a common reference point or voltage level against which other voltages are measured. It serves as a point of reference for electrical potential and is typically designated as the zero-voltage point. The circuit symbol for ground is shown in Figure 2.1.

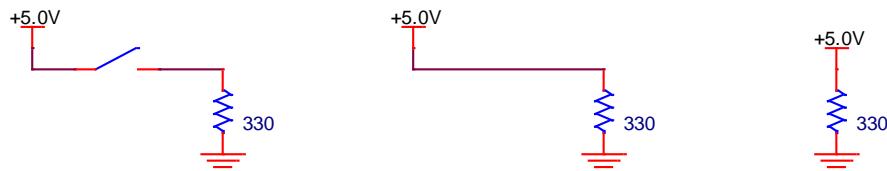

Figure 2. 1

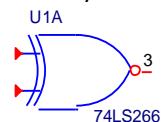

#### DC VOLTAGE SOURCE

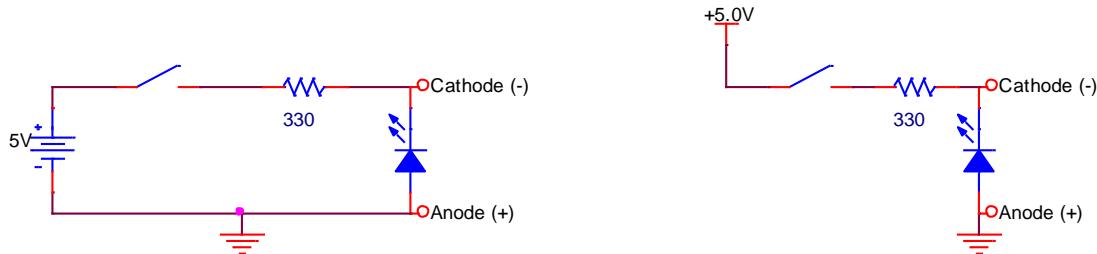

A DC voltage source is a device that provides the appropriate DC voltage required by the device to function. 5 voltages (5V or +5.0V) are commonly used in digital systems. Two DC voltage source schematic symbols are shown in Figure 2.2.

Figure 2. 2

#### RESISTOR

A resistor is an electronic component that limits the flow of electric current in a circuit. A resistor schematic symbol is shown in Figure 2.3. The number next to the symbol tells the reader that the resistance is 330 ohms ( $330\Omega$ ) or 1000 ohms ( $1k\Omega$ ). Sometimes the unit symbol ' $\Omega$ ' is left out on schematics.

Figure 2. 3

## SWITCH

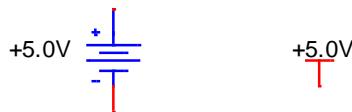

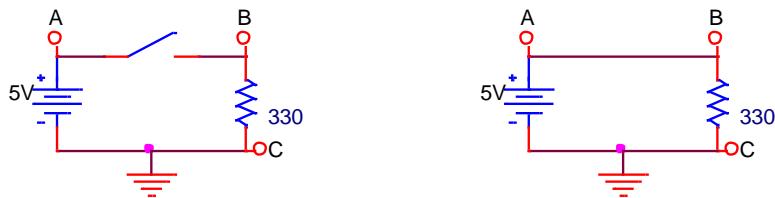

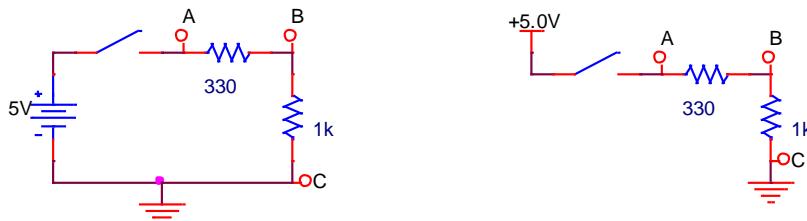

A switch, as shown in Figure 2.3, is a simple circuit component used to control the flow of electricity.

Figure 2. 4

It is typically used to manually open or close a circuit, allowing or preventing the current from flowing through the circuit as shown in Figure 2.4.

Figure 2.5: Switch Open and Switch Closed

Figure 2.4 shows another way to draw the circuits in Figure 2.5. This method is preferred in digital logic and will be used throughout this lab manual. Typically, the positive voltages are towards the top of the schematic and ground is at the bottom.

Figure 2.6: Switch Open and Switch Closed

## OHM'S LAW

When a voltage is applied across a resistor, the current flowing through the resistor can be calculated using Ohm's Law:

$$V = IR \Leftrightarrow I = \frac{V}{R}$$

Ohm's Law states that the current ( $I$ ) flowing through a resistor is directly proportional to the voltage ( $V$ ) applied across it and inversely proportional to the resistance ( $R$ ) of the resistor.

### EXAMPLE 1.1

Find the current flowing through and the voltage across the  $330\Omega$  resistor when the switch is closed and open.

#### SOLUTION

Since the DC voltage is  $V = 5V$  and the resistor has a resistance of  $R = 330\Omega$ , therefore by Ohm's Law:

$$I = \frac{V}{R} = \frac{5V}{330\Omega} = 15.15mA$$

$$V = IR = (15.15mA)(330\Omega) \cong 5V$$

Thus, the current flowing through the circuit is 15.15 milliampere or 15.15mA. The voltage across the resistor is equal to the DC voltage source. When the switch is open,  $I = 0A$ , and therefore the voltage across the resistor is:

$$V = IR \rightarrow 0V = 0A(330\Omega)$$

When the switch is Open, node A has a voltage of 5V, and both nodes B and C have voltages of 0V. However, when the switch is closed, both A and B are 5V and C remains at 0V. The voltage across the Resistors is the difference between the voltage at Node B and at Node C.

$$V_{BC} = V_B - V_C \rightarrow 5V_B - 0V_C = 5V_{BC}.$$

| Switch State | Node A, $V_A$ | Node B, $V_B$ | Node C, $V_C$ | Node B to C, $V_{BC}$ |

|--------------|---------------|---------------|---------------|-----------------------|

| Open         | 5V            | 0V            | 0V            | 0V                    |

| Closed       | 5V            | 5V            | 0V            | 5V                    |

## LED

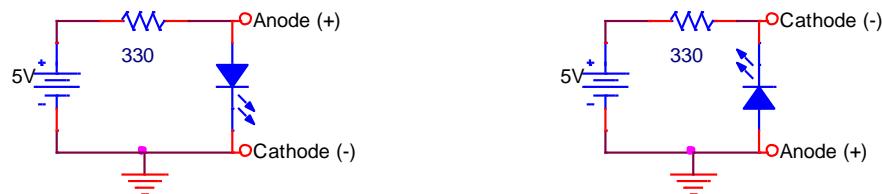

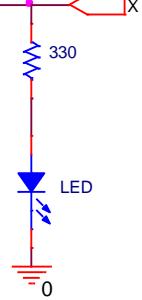

A diode is an electronic component that allows electric current to flow in one direction while blocking it in the opposite direction. It acts as a “one-way valve” for electrical current. The diode’s terminals are called the anode (+) and cathode (-). An LED (Light-Emitting Diode) is a specific type of diode that emits light when current passes through it. It is designed to convert electrical energy into light energy. The LED schematic symbol is show in Figure 2.6.

Figure 2. 7: LED

When the voltage across a diode is applied in the forward direction (anode connected to the positive terminal and cathode connected to the negative terminal), it allows current to flow easily, similar to a closed switch. This is known as the forward bias.

| LED    | Forward Voltage, $V_f$ |

|--------|------------------------|

| Red    | 1.8V – 2.2V            |

| Orange | 2.0V – 2.2V            |

| Yellow | 2.0V – 2.2V            |

| Green  | 2.0V – 3.5V            |

| Blue   | 2.5V – 3.7V            |

| White  | 2.5V – 3.7V            |

Table 2. 1: LED Forward Voltages

On the other hand, when the voltage is applied in the reverse direction (anode connected to the negative terminal and cathode connected to the positive terminal), the diode blocks the current flow, acting as an open switch. This is known as the reverse bias.

Figure 2. 8: Circuit with LED and Resistor

### EXAMPLE 1.2

Find the current flowing through the circuit if the LED has a forward voltage is  $V_f = 2V$ .

#### SOLUTION

Since  $V = 5V$ ,  $V_f = 2V$ , and  $R = 330\Omega$ , therefore by Ohm's Law:

$$I = \frac{(V-V_f)}{R} = \frac{5V-2V}{330\Omega} = \frac{3V}{330\Omega} = 9.09mA.$$

Thus, the current flowing through the circuit is 9.09 milliampere or 9.09mA. Also note that the voltage across the resistor is 3V.

$$5V = 2V + 3V.$$

### PRELIMINARY PROCEDURE

1. Read the lab.

2. Research resistors, switches, LEDs, breadboards, DC power supplies, and logic gates. Briefly paraphrase your findings. This will help you understand the topics presented in this lab. In addition, when you write your lab report, use your research as the theory section of your report. You may include images, graphs, equations, etc.

### PROCEDURE

1. Measure the resistance of one  $330\Omega$  and  $1k\Omega$  resistor. Record the measured values in Table 2.2. It's a good habit to measure your resistors' values before you place them into your circuit.

| Resistor, $\Omega$ | Measured, $\Omega$ |

|--------------------|--------------------|

| $330\Omega$        |                    |

| $1k\Omega$         |                    |

Table 2. 2

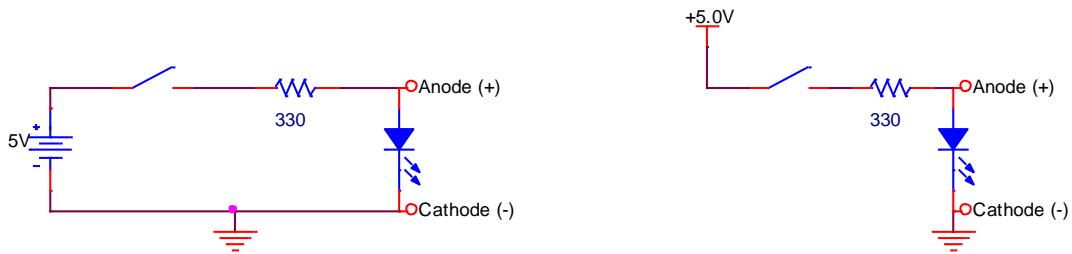

2. Build Figure 2.9 on a breadboard. If switches are not available, then one can emulate a switch by using a wire. Measure and record the voltages across each resistor when the switch is open and closed. Observe that  $V_{AB} + V_{BC} = V_{AC} = V_{Supply}$  when resistors are connected in series.

Figure 2. 9

| Switch State | Measured, $V_{Supply}$ | Measured, $V_{AB}$ | Measured, $V_{BC}$ | Measured, $V_{AC}$ |

|--------------|------------------------|--------------------|--------------------|--------------------|

| Open         |                        |                    |                    |                    |

| Closed       |                        |                    |                    |                    |

Table 2. 3

3. Modify your circuit by replacing the  $1k\Omega$  resistor with an LED, as shown in Figure 2.10. Measure and record the

voltage across the resistor as well as the LED's forward voltage,  $V_f$  (anode to cathode). Observe that  $V_f + V_R = V_{DC} = 5V$ .

Figure 2. 10

| Switch State | Forward Voltage, $V_f$ | Voltage across Resistor, $V_R$ | LED State (On or off) |

|--------------|------------------------|--------------------------------|-----------------------|

| Open         |                        |                                |                       |

| Closed       |                        |                                |                       |

Table 2. 4

4. Open the switch and insert your LED in the other direction so that it's reverse bias. When the switch is closed, is the LED on or off? Notice that  $V_{rev} = V_{Supply} = 5V$  when the switch is closed.

Figure 2. 11

| Switch State | Forward Voltage, $V_{rev}$ | Voltage across Resistor, $V_R$ | LED State (On or off) |

|--------------|----------------------------|--------------------------------|-----------------------|

| Open         |                            |                                |                       |

| Closed       |                            |                                |                       |

Table 2. 5

5. Close the switch and turn the LED around so that the LED turns on. Measure the forward voltage and voltage across the resistor for each LED color.

| LED    | Forward Voltage, $V_f$ | Voltage across Resistor, $V_R$ |

|--------|------------------------|--------------------------------|

| Red    |                        |                                |

| Orange |                        |                                |

| Yellow |                        |                                |

| Green  |                        |                                |

| Blue   |                        |                                |

| White  |                        |                                |

Table 2. 6

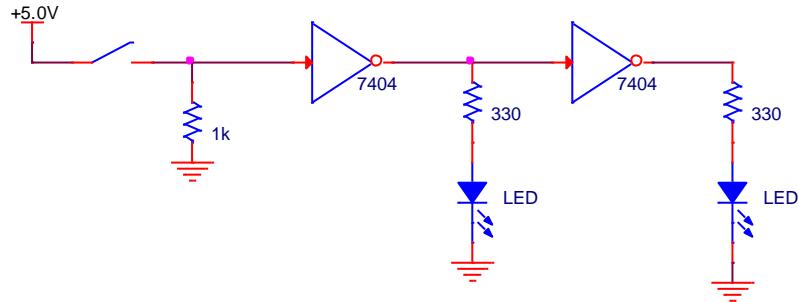

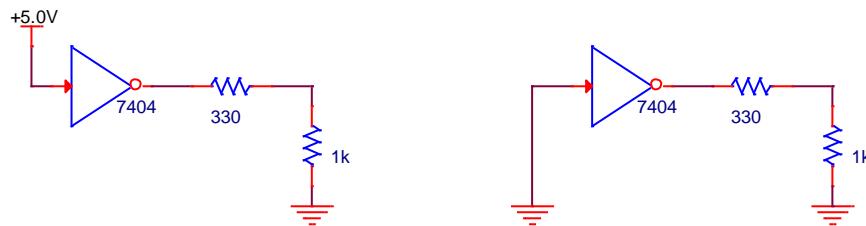

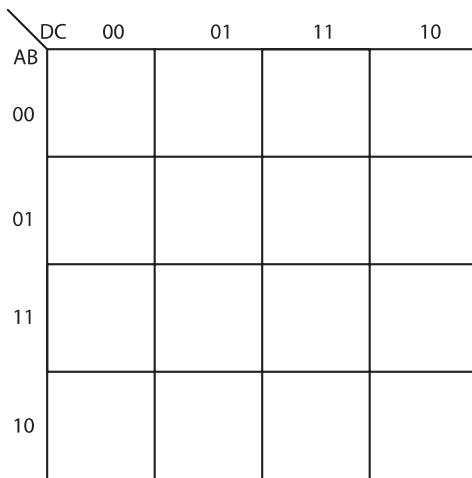

6. Connect two inverters in series (cascade) as shown in Figure 2.12. Check the logic when the input is connected

to 5V, open (not connected to anything), and 0V (Ground). Record your observations for these three cases in Table 2.7.

Figure 2. 12

| Wire State      | LED 1, (On or off) | LED 2, (On or off) |

|-----------------|--------------------|--------------------|

| 5V              |                    |                    |

| Open (Floating) |                    |                    |

| 0V, Ground      |                    |                    |

Table 2. 7

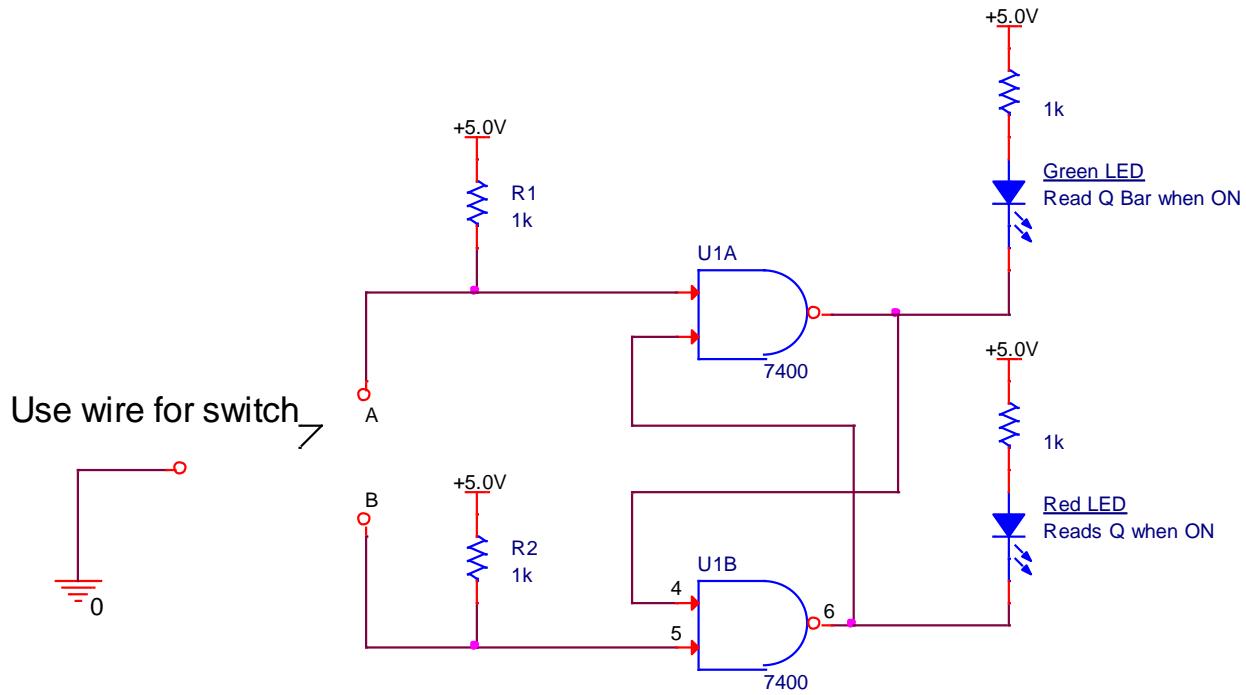

7. Connect the two inverters as cross-coupled inverters as shown in Figure 2.13. This is a basic latch circuit, the most basic form of memory. This arrangement is not the best way to implement a latch but serves to illustrate the concept (you will study latch circuits in more detail later). Check the logic when the input is connected to 5V, open (not connected to anything), 0V (Ground), and back to open. Record your observations for these three cases in Table 2.8.

Figure 2. 13

| Wire State      | LED, (On or off) |

|-----------------|------------------|

| 5V              |                  |

| Open (Floating) |                  |

| 0V              |                  |

| Open (Floating) |                  |

Table 2. 8

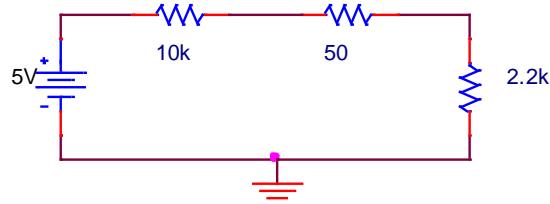

## EVALUATION AND REVIEW QUESTIONS

1. In Figure 2.9, we noticed that  $V_{AB} + V_{BC} = V_{AC} = V_{DC}$ . Therefore, ohm's law can be expanded to  $(V_{AB} + V_{BC}) = (R_{AB} + R_{BC})(I)$ . Find the current flowing through circuit. The same current flows through  $R_{AB}$  and  $R_{BC}$ .

2. Find the current flowing through circuit then the voltage across each resistor.

Figure 2. 14

3. According to your measurements in step 5, which LED has the least and most amount of current flowing through it?

4. Find the current flowing through and the voltages across each resistor in Figure 2.15.

Figure 2. 15

# Logic Gates and Pull-Up and Pull-Down Resistors

## OBJECTIVES

After completing this experiment, you will be able to

- Experimentally verify the truth tables for the NAND and NOR, and inverter gates.

- Use the NAND and NOR gates to formulate other basic logic gates.

## MATERIALS NEEDED

- 7400 quad 2-input NAND gate

- 7402 quad 2-input NOR gate

- 7404 NOT gate (inverter)

- DMM probes

## THEORY

### LOGIC GATES

Logic gates are the basic building blocks of digital electronic circuits. They are devices that perform a specific logic operation on one or more input signals and produce a single output signal. The most basic logic gates are the NOT gate, AND gate, OR gate, and XOR (exclusive OR) gate. These gates can be combined to create more complex circuits that perform more advanced logic operations.

### UNIVERSAL LOGIC GATES

There are three types of logic gates that are considered to be "universal" because they can be combined to create any other logic gate or digital circuit. These universal gates are:

- NAND (NOT-AND) gate: This gate performs the opposite function of an AND gate, meaning it produces a low output (0) if all of its inputs are high, and a high output (1) otherwise.

- NOR (NOT-OR) gate: This gate performs the opposite function of an OR gate, meaning it produces a high output (1) if all of its inputs are low, and a low output (0) otherwise.

- NOT gate (inverter): As the name suggests, it inverts the input signal, so that a high input (1) produces a low output (0), and vice versa.

- Since NAND and NOR gates are universal gates, any logic circuit can be implemented using only NAND gates, or only NOR gates.

### TTL (TRANSISTOR-TRANSISTOR LOGIC)

TTL (Transistor-Transistor Logic) is a type of digital logic circuit that uses transistors to switch between the two logic levels of 0 and 1.

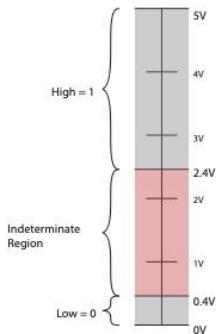

Figure 3. 1: TTL Switching Voltages

As shown in Figure 3.1, the logic HIGH or binary '1' level is typically represented by a voltage between 2.4V-5V, while the logic LOW or binary '0' level is represented by a voltage between 0V-0.4V. The exact voltage levels may vary depending on the specific type of TTL circuit.

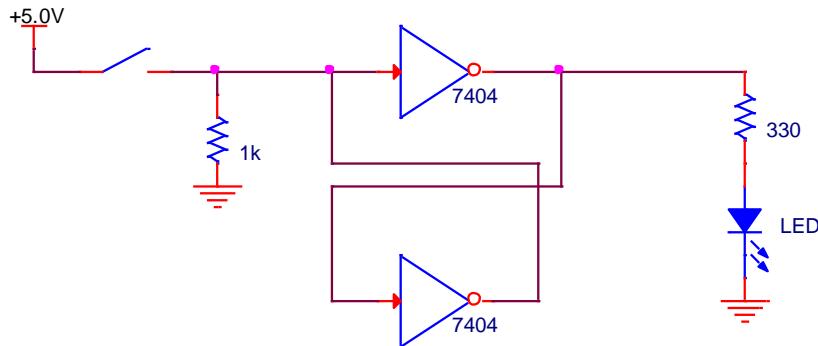

## HOW TO CREATE INPUT SIGNALS IN THE LAB

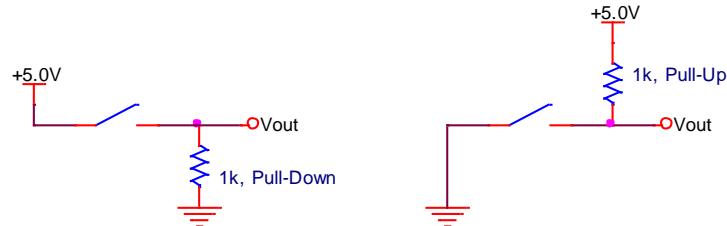

Pull-down and pull-up resistors are used in electronic circuits to establish a known or defined voltage level when a switch is open. They are typically used in digital circuits to prevent floating or undefined states that could lead to unreliable or incorrect readings.

Figure 3.2

### PULL-DOWN RESISTOR

A pull-down resistor is connected between the signal line and ground. When the switch is open, the pull-down resistor ensures that the voltage is "pulled down" to a LOW level (e.g., 0 volts or ground). This establishes a clear "off" or "0" state for the signal.

### PULL-UP RESISTOR

On the other hand, a pull-up resistor is connected between the signal line and a positive voltage source (e.g., Vcc or +5 volts). When the switch is open, the pull-up resistor "pulls" the voltage up to a high level (e.g., 5 volts). This establishes a clear "on" or "1" state for the signal.

When the switch is closed, the pull-down or pull-up resistor has little effect as the switch takes precedence and overrides the resistor's influence on the signal voltage level.

| Switch State | $V_{in}$  |         |

|--------------|-----------|---------|

|              | Pull-Down | Pull-Up |

| Open         | 0V, '0'   | 5V, '1' |

| Closed       | 5V, '1'   | 0V, '0' |

Table 3.1

In digital circuits, it's important to have a well-defined voltage level to ensure reliable signal interpretation by the receiving circuitry (such as microcontrollers or logic gates).

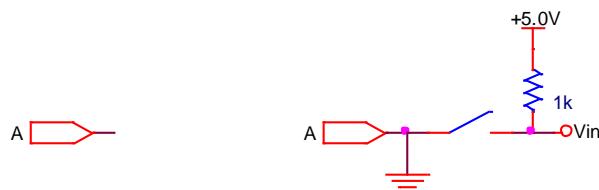

## NAMING PORTS ON A SCHEMATIC

To simplify the schematic, we can replace the entire pull-up or pull-down network with just the port.

Figure 3.3

## PRELIMINARY PROCEDURE

1. Read the lab.

2. Number the pins on the gates of each circuit in the procedure.

3. Determine the Prelab X output (1 or 0) column corresponding to each figure in the procedure.

## PROCEDURE

1. Build Figure 3.# on a breadboard and use either a switch or a wire to implement the switch. Measure the voltage at node  $V_{out}$  when the switch is open and closed.

| Switch State | Pull-Down, Voltage, $V_{in}$ | Binary Value, (1 or 0) | Pull-Up, Voltage, $V_{in}$ | Binary Value, (1 or 0) |

|--------------|------------------------------|------------------------|----------------------------|------------------------|

| Open         |                              |                        |                            |                        |

| Close        |                              |                        |                            |                        |

Table 3. 2

2. Build the following circuits and complete their corresponding table. Use a DMM to measure and record the output voltage for each input combination, as well as determine its binary representation.

- a. Figure 3.4 through 3.13 and Table 3.3 through 3.12, respectively.

Figure 3. 4

| Inputs | Output |   |           |   |                         |

|--------|--------|---|-----------|---|-------------------------|

|        | A      | B | Prelab, X | X | Measured Output Voltage |

| 0 0    |        |   |           |   |                         |

| 0 1    |        |   |           |   |                         |

| 1 0    |        |   |           |   |                         |

| 1 1    |        |   |           |   |                         |

Table 3. 3

Figure 3. 5

| Inputs | Output |   |           |   |                         |

|--------|--------|---|-----------|---|-------------------------|

|        | A      | B | Prelab, X | X | Measured Output Voltage |

| 0 0    |        |   |           |   |                         |

| 0 1    |        |   |           |   |                         |

| 1 0    |        |   |           |   |                         |

|   |   |  |  |  |

|---|---|--|--|--|

| 1 | 1 |  |  |  |

|---|---|--|--|--|

Table 3. 4

Figure 3. 6

| Inputs | Prelab Output | Output | Measured Output Voltage |

|--------|---------------|--------|-------------------------|

| A      | X             | X      |                         |

| 1      |               |        |                         |

| 0      |               |        |                         |

Table 3. 5

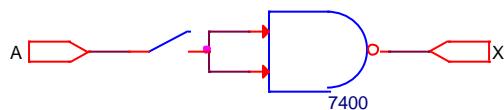

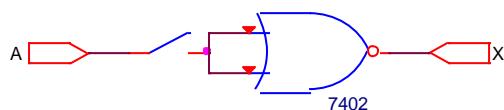

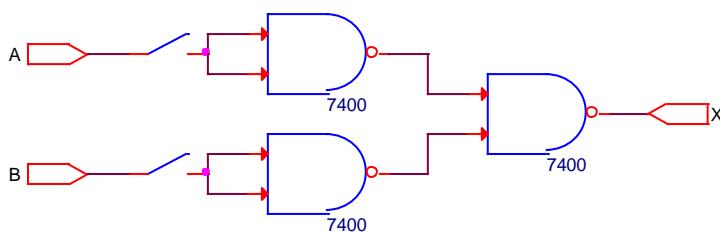

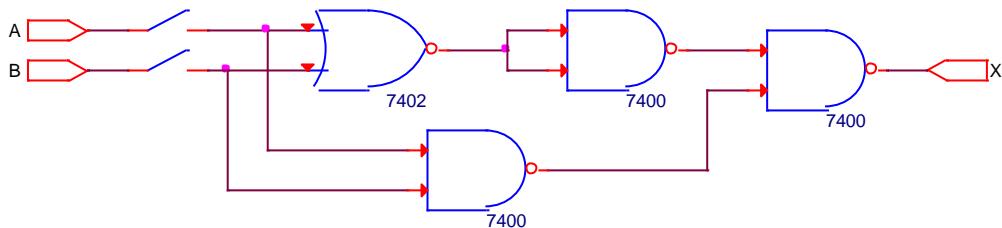

Figure 3. 7

| Inputs | Prelab Output | Output | Measured Output Voltage |

|--------|---------------|--------|-------------------------|

| A      | X             | X      |                         |

| 1      |               |        |                         |

| 0      |               |        |                         |

Table 3. 6

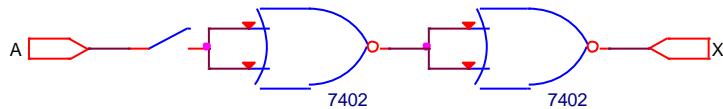

Figure 3. 8

| Inputs | Prelab Output | Output | Measured Output Voltage |

|--------|---------------|--------|-------------------------|

| A      | X             | X      |                         |

| 1      |               |        |                         |

| 0      |               |        |                         |

Table 3. 7

Figure 3. 9

| Inputs | Prelab Output | Output | Measured Output Voltage |

|--------|---------------|--------|-------------------------|

| A      | X             | X      |                         |

| 1      |               |        |                         |

| 0      |               |        |                         |

Table 3. 8

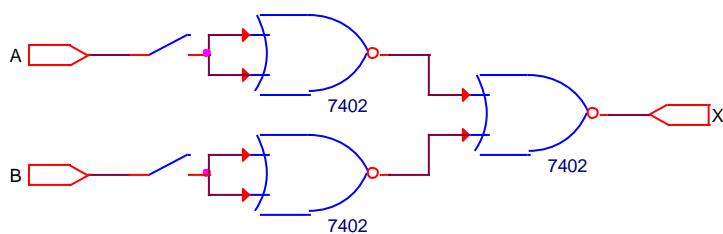

Figure 3. 10

| Inputs |   | Output    |   |                         |

|--------|---|-----------|---|-------------------------|

| A      | B | Prelab, X | X | Measured Output Voltage |

| 0      | 0 |           |   |                         |

| 0      | 1 |           |   |                         |

| 1      | 0 |           |   |                         |

| 1      | 1 |           |   |                         |

Table 3. 9

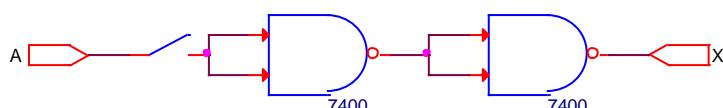

Figure 3. 11

| Inputs |   | Output    |   |                         |

|--------|---|-----------|---|-------------------------|

| A      | B | Prelab, X | X | Measured Output Voltage |

| 0      | 0 |           |   |                         |

| 0      | 1 |           |   |                         |

| 1      | 0 |           |   |                         |

| 1      | 1 |           |   |                         |

Table 3. 10

Figure 3. 12

| Inputs |   | Output    |   |                         |

|--------|---|-----------|---|-------------------------|

| A      | B | Prelab, X | X | Measured Output Voltage |

| 0      | 0 |           |   |                         |

| 0      | 1 |           |   |                         |

| 1      | 0 |           |   |                         |

| 1      | 1 |           |   |                         |

Table 3. 11

Figure 3. 13

| Inputs |   | Output    |   |                         |

|--------|---|-----------|---|-------------------------|

| A      | B | Prelab, X | X | Measured Output Voltage |

| 0      | 0 |           |   |                         |

| 0      | 1 |           |   |                         |

| 1      | 0 |           |   |                         |

| 1      | 1 |           |   |                         |

Table 3. 12

### EVALUATION AND REVIEW QUESTIONS

1. Look over the truth tables in your report.

- a. Draw the circuits that are equivalent to the inverter.

- b. Draw the circuit that is equivalent to the AND gate.

- c. Draw the circuit that is equivalent to the OR gate.

2. Assume you were troubleshooting a circuit containing a 4-input NAND gate and you discover that the output of the NAND gate is always HIGH. Is this an indication of a bad gate? Explain your answer.

## Boolean Laws And DeMorgan's Theorems

### OBJECTIVES

After completing this experiment, you will be able to

- Experimentally verify several of the rules for Boolean algebra.

- Design circuits to prove Rules 10 and 11.

- Experimentally determine the truth tables for circuits with three input variables, and use DeMorgan's theorem to prove algebraically whether they are equivalent.

### MATERIALS NEEDED

- 7432 quad 2-input OR gate

- 7404 hex inverter

- 7408 quad 2-input AND gate

- One  $1k\Omega$  resistor

- One LED

- Two oscilloscope probes

- One function generator probe

### THEORY

#### BOOLEAN ALGEBRA

Boolean algebra is a mathematical system that is used to represent and manipulate logical expressions. It is based on the two values of true and false (or 1 and 0), and includes operations such as AND, OR, and NOT. Boolean algebra is used in computer science and electrical engineering to design and analyze digital circuits. It is also used in mathematical logic and in the study of algorithms and complexity theory.

#### BASIC RULES OF BOOLEAN ALGEBRA

1.  $A + 0 = A$

2.  $A + 1 = 1$

3.  $A \cdot 0 = 0$

4.  $A \cdot 0 = 0$

5.  $A + A = A$

6.  $A + \bar{A} = 1$

7.  $A \cdot A = A$

8.  $A \cdot \bar{A} = 0$

9.  $\bar{\bar{A}} = A$

10.  $A + AB = A$

11.  $A + \bar{A}B = A + B$

12.  $(A + B)(A + C) = A + BC$

### PRELIMINARY PROCEDURE

1. Read the lab.

2. Number the pins of each gate in all the circuits in the procedure.

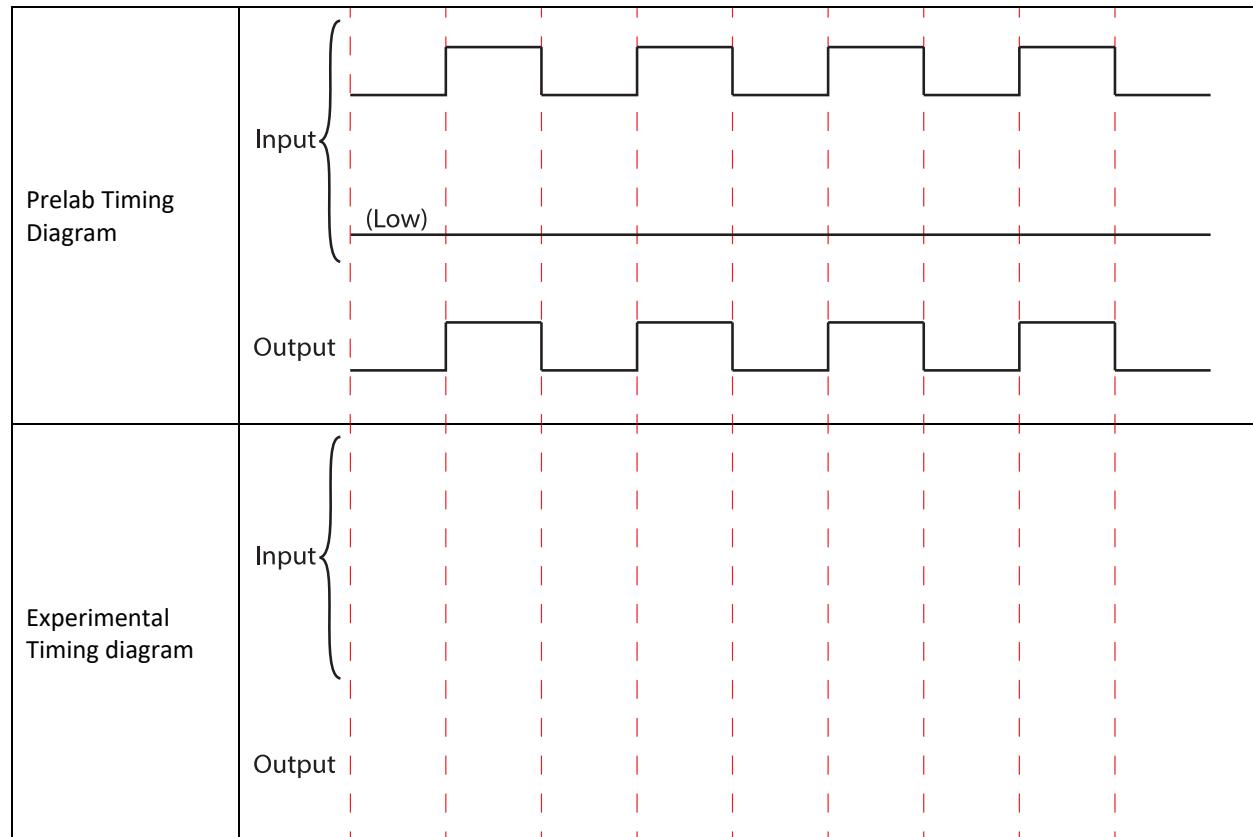

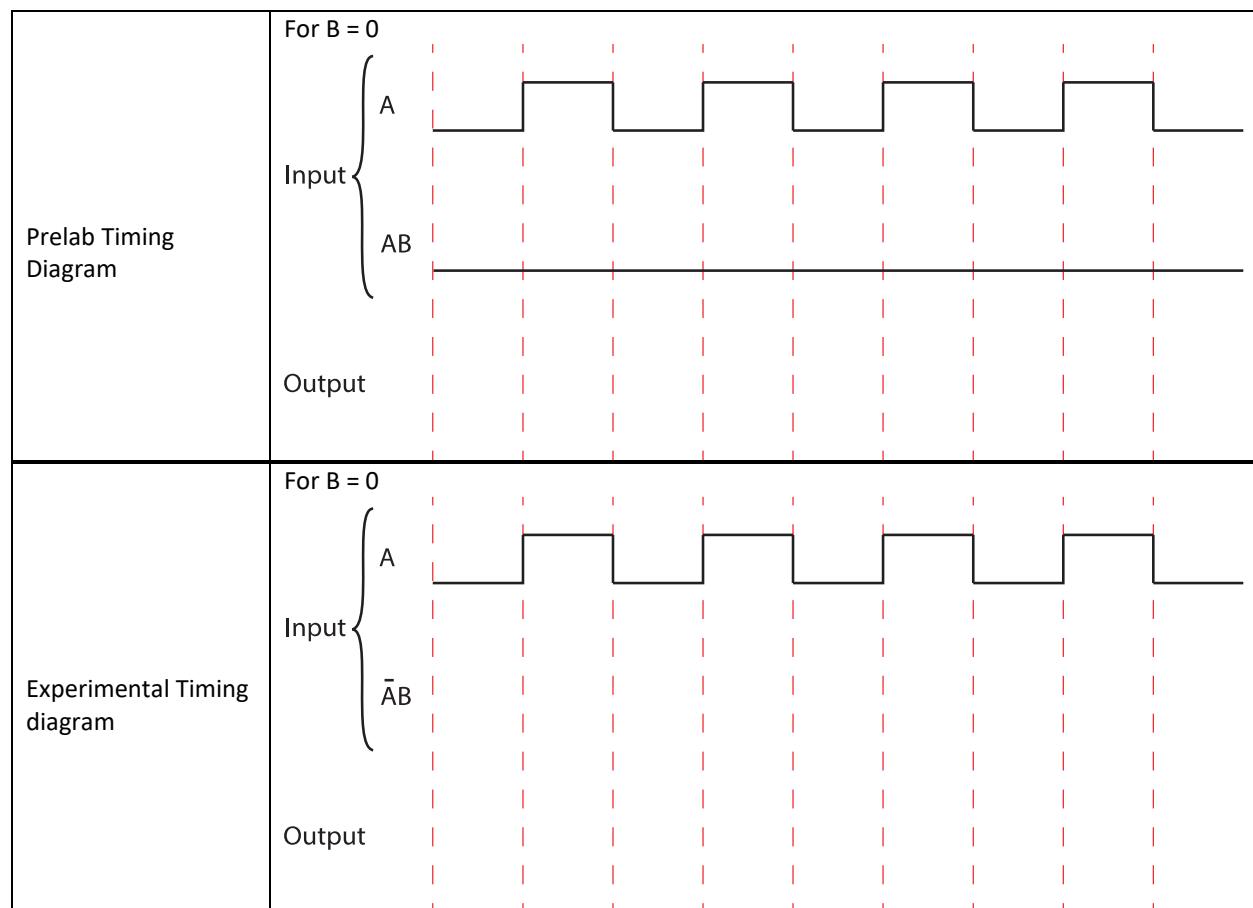

3. Complete the Prelab Timing Diagrams for Table 3.1 through Table 3.6.

- a. Figure 3.5 and 3.6 must be designed before completing the Prelab Timing Diagram.

4. Complete the Prelab X column for Table 3.9 and Table 3.10.

## PROCEDURE

---

### FOR FIGURES 4.1 THROUGH 4.4:

1. Build the circuit on a breadboard.

2. Complete the experimental timing diagram.

3. Determine the Boolean rule.

4. Compare prelab and experimental timing diagrams.

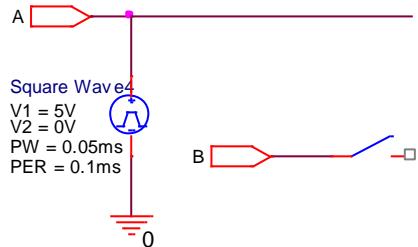

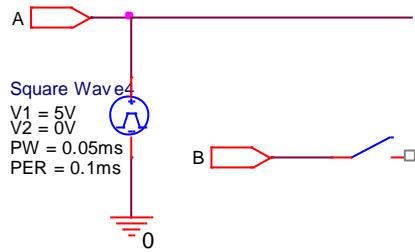

### FUNCTION GENERATOR SETTINGS:

1.  $5V_{pp}$  square wave

2. 2.5V DC off set (This will make your square wave vary from 0V to 5V rather than -2.5V to 2.5V)

3. 10k Hz frequency

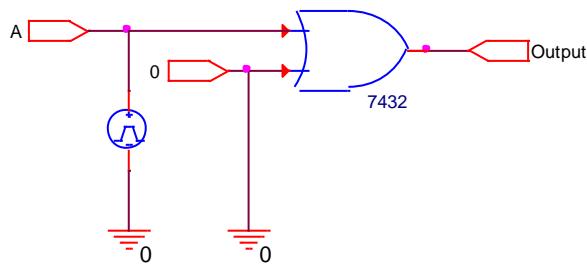

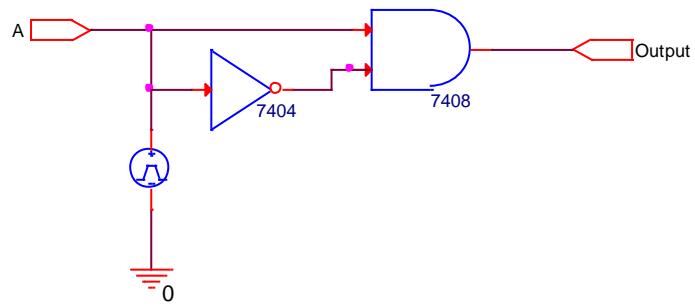

Figure 4. 1

|              |             |

|--------------|-------------|

| Boolean Rule | $A + 0 = A$ |

|--------------|-------------|

Table 4. 1

Figure 4. 2

|                             |                            |

|-----------------------------|----------------------------|

| Prelab Timing Diagram       | <p>Input</p> <p>Output</p> |

| Experimental Timing diagram | <p>Input</p> <p>Output</p> |

| Boolean Rule                |                            |

Table 4. 2

Figure 4. 3

|                             |                 |

|-----------------------------|-----------------|

| Prelab Timing Diagram       | Input<br>Output |

| Experimental Timing diagram | Input<br>Output |

| Boolean Rule                |                 |

Table 4. 3

Figure 4. 4

|                             |                            |

|-----------------------------|----------------------------|

| Prelab Timing Diagram       | <p>Input</p> <p>Output</p> |

| Experimental Timing diagram | <p>Input</p> <p>Output</p> |

| Boolean Rule                |                            |

Table 4. 4

**FOR FIGURE 4.5 AND 4.6:**

1. Draw and complete the circuit representation of rule 10 and 11.

2. Build the circuit on a breadboard.

3. Complete the experimental timing diagram.

4. Compare prelab and experimental timing diagrams.

**RULE 10:  $A + AB = A$**

Figure 4.5

Table 4.5

|                             |                                                                                                                                                                                                 |

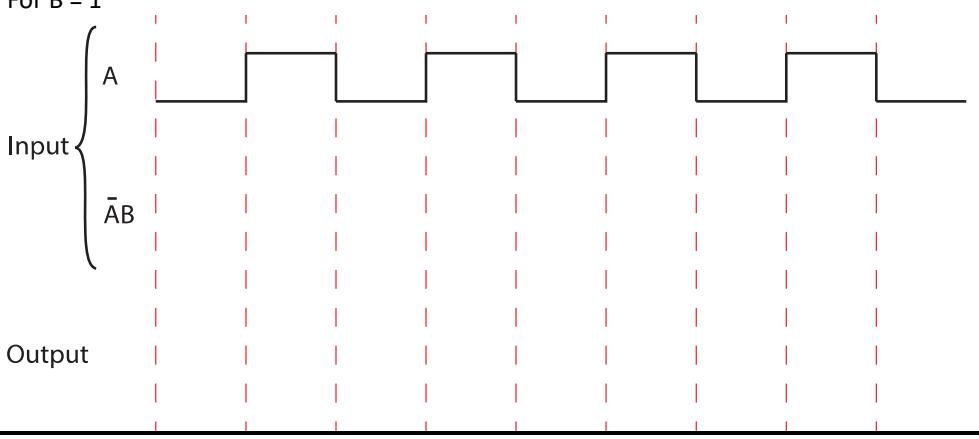

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prelab Timing Diagram       | <p>For <math>B = 1</math></p>  <p>Input</p> <p><math>A</math></p> <p><math>\bar{A}B</math></p> <p>Output</p>  |

| Experimental Timing diagram | <p>For <math>B = 1</math></p>  <p>Input</p> <p><math>A</math></p> <p><math>\bar{A}B</math></p> <p>Output</p> |

Table 4. 6

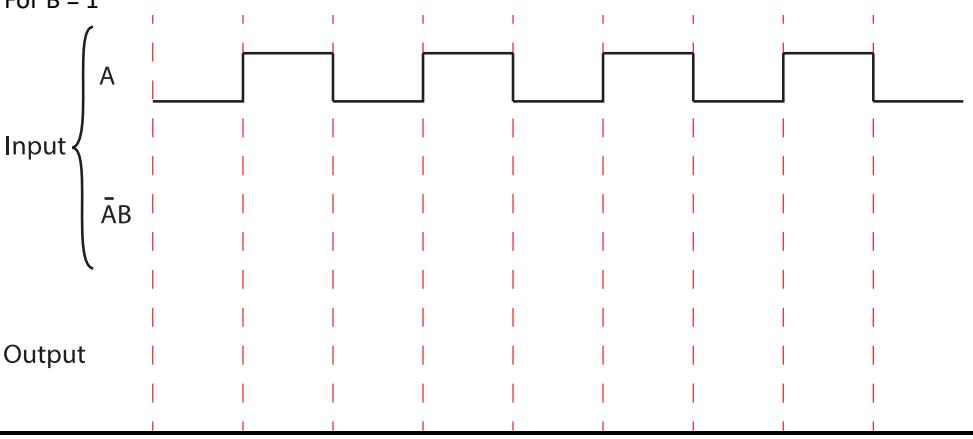

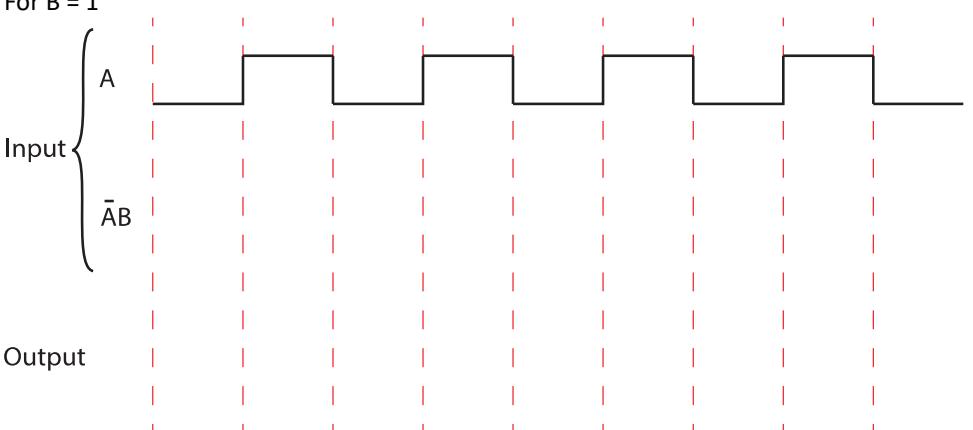

**RULE 11:  $A + \bar{A}B = A + B$**

Figure 4. 6

|                             |           |                                                                                                                                                                                                                                                                                                       |

|-----------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Prelab Timing Diagram       | For B = 0 | <p>Input { A, <math>\bar{A}B</math> }<br/>Output</p> <p>Detailed description: This timing diagram shows a square wave A (5V high, 0V low) and its complement <math>\bar{A}</math> (0V high, 5V low). The output is the NOR of A and <math>\bar{A}</math>, which is always 5V (high).</p>              |

|                             | For B = 1 | <p>Input { A, <math>\bar{A}B</math> }<br/>Output</p> <p>Detailed description: This timing diagram shows a square wave A (5V high, 0V low) and its complement <math>\bar{A}</math> (0V high, 5V low). The output is the NOR of A and <math>\bar{A}</math>, which is always 5V (high).</p>              |

| Experimental Timing diagram | For B = 0 | <p>Input { A, <math>\bar{A}B</math> }<br/>Output</p> <p>Detailed description: This experimental timing diagram shows a square wave A (5V high, 0V low) and its complement <math>\bar{A}</math> (0V high, 5V low). The output is the NOR of A and <math>\bar{A}</math>, which is always 5V (high).</p> |

|                             | For B = 1 | <p>Input { A, <math>\bar{A}B</math> }<br/>Output</p> <p>Detailed description: This experimental timing diagram shows a square wave A (5V high, 0V low) and its complement <math>\bar{A}</math> (0V high, 5V low). The output is the NOR of A and <math>\bar{A}</math>, which is always 5V (high).</p> |

Table 4. 7

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

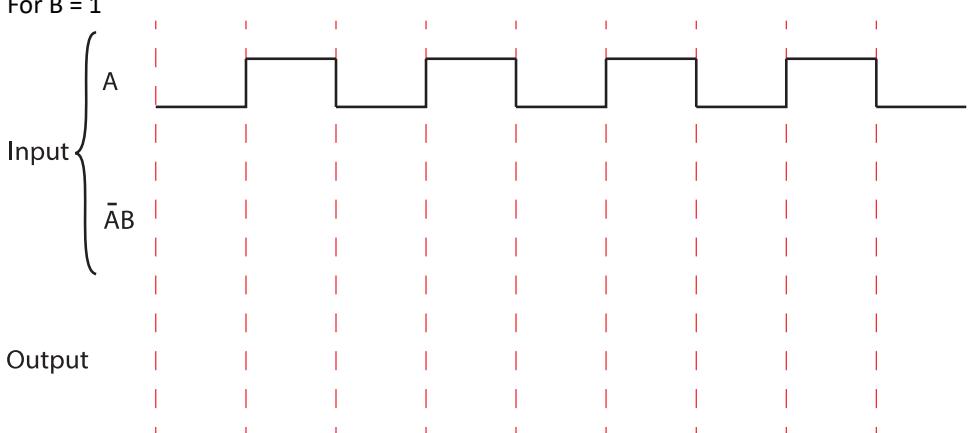

| Prelab Timing Diagram       | <p>For <math>B = 1</math></p>  <p>Input</p> <p><math>A</math></p> <p><math>\bar{A}B</math></p> <p>Output</p> <p>Detailed description: This timing diagram shows two inputs and one output. The input <math>A</math> is a square wave with a period of 4 units. The input <math>\bar{A}B</math> is a square wave with a period of 4 units, starting at 1. The output is a square wave with a period of 4 units, starting at 0. Red dashed vertical lines are present at the start of each period.</p>  |

| Experimental Timing diagram | <p>For <math>B = 1</math></p>  <p>Input</p> <p><math>A</math></p> <p><math>\bar{A}B</math></p> <p>Output</p> <p>Detailed description: This timing diagram shows two inputs and one output. The input <math>A</math> is a square wave with a period of 4 units. The input <math>\bar{A}B</math> is a square wave with a period of 4 units, starting at 1. The output is a square wave with a period of 4 units, starting at 0. Red dashed vertical lines are present at the start of each period.</p> |

Table 4. 8

## MORE CIRCUITS

Build the following circuits and complete their corresponding table. Record the state of the LED, as well as determine its binary representation. Figure 4.7 – 4.8 and Table 4.9 – 4.10, respectively.

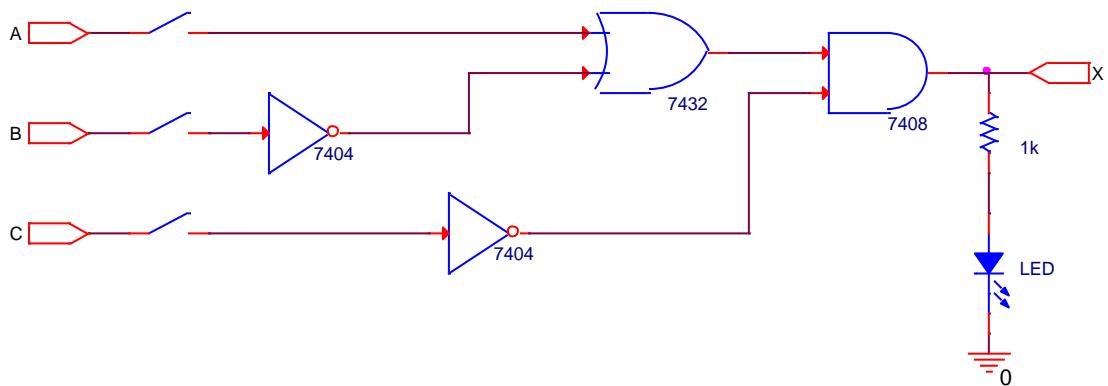

Figure 4. 7

| Inputs |   |   | Prelab Output | Output | LED<br>(On or Off) |

|--------|---|---|---------------|--------|--------------------|

| A      | B | C | X             | X      |                    |

| 0      | 0 | 0 |               |        |                    |

| 0      | 0 | 1 |               |        |                    |

| 0      | 1 | 0 |               |        |                    |

| 0      | 1 | 1 |               |        |                    |

| 1      | 0 | 0 |               |        |                    |

| 1      | 0 | 1 |               |        |                    |

| 1      | 1 | 0 |               |        |                    |

| 1      | 1 | 1 |               |        |                    |

Table 4. 9

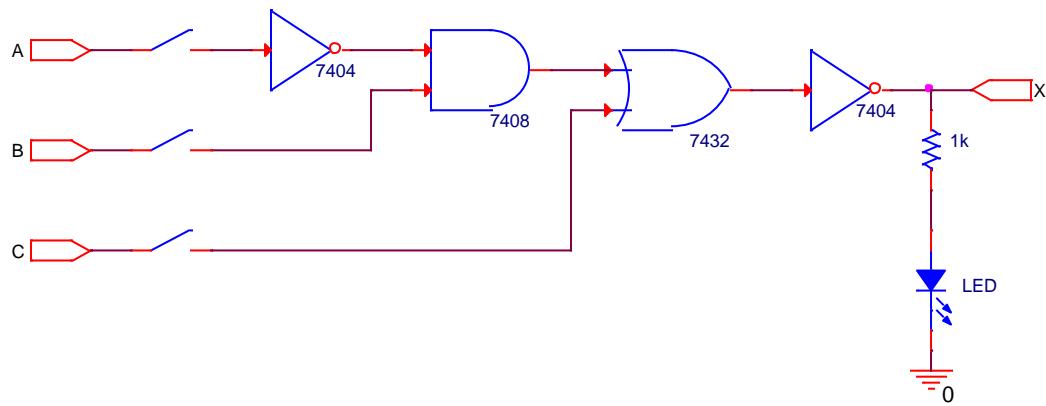

Figure 4.8

| Inputs |   |   | Prelab Output | Output | LED<br>(On or Off) |

|--------|---|---|---------------|--------|--------------------|

| A      | B | C | X             | X      |                    |

| 0      | 0 | 0 |               |        |                    |

| 0      | 0 | 1 |               |        |                    |

| 0      | 1 | 0 |               |        |                    |

| 0      | 1 | 1 |               |        |                    |

| 1      | 0 | 0 |               |        |                    |

| 1      | 0 | 1 |               |        |                    |

| 1      | 1 | 0 |               |        |                    |

| 1      | 1 | 1 |               |        |                    |

Table 4.10

## EVALUATION AND REVIEW QUESTIONS

---

1. The equation  $X = A(A + B) + C$  is equivalent to  $X = A + C$ . Prove this with Boolean algebra.

2. Show how to implement the logic in Question 1 with NOR gates.

3. Draw two equivalent circuits that could prove Rule 12. Show the left side of the equation as one circuit and the right side as another circuit.

4. Determine whether the circuits in Figures 4.7 and 4.8 perform equivalent logic. Then, using DeMorgan's theorem, prove your answer.

5. Write the Boolean expression for the circuit shown in Figure 4.9. Then, using DeMorgan's theorem, prove that the circuit is equivalent to that shown in Figure 4.1.

Figure 4.9

# Logic Circuit Simplification

## OBJECTIVES

After completing this experiment, you will be able to

- Develop the truth table for a BCD invalid code detector.

- Use a Karnaugh map to simplify the expression.

- Build and test a circuit that implements the simplified expression.

- Predicts the effect of “faults” in the circuit.

## MATERIALS NEEDED

- 7400 NAND gate

- LED

- One  $330\Omega$  resistor

- One  $3.3k\Omega$  resistor

## THEORY

### KARNAUGH MAPS

Karnaugh maps are graphical representations of Boolean algebra expressions that are used to simplify logic circuits. They provide a visual way to group together terms in a Boolean expression that have a similar logical structure, making it easier to identify and simplify the expression. The map consists of a grid of squares, each representing a single term in the Boolean expression, with the value of the term indicated by the color or shading of the square. The squares are arranged in a specific pattern, such as a circle or a rectangle, to make it easy to identify and group together adjacent terms that have similar logical structure.

### BCD (BINARY-CODED DECIMAL)

BCD (Binary-Coded Decimal) is a way to represent decimal numbers using binary digits (bits). In BCD, each decimal digit (0-9) is represented by a four-bit binary number, allowing for a total of 10 unique combinations of bits.

| Decimal | Binary-Coded Decimal |

|---------|----------------------|

| 0       | 0000                 |

| 1       | 0001                 |

| 2       | 0010                 |

| 3       | 0011                 |

| 4       | 0100                 |

| 5       | 0101                 |

| 6       | 0110                 |

| 7       | 0111                 |

| 8       | 1000                 |

| 9       | 1001                 |

Table 5. 1: Decimal to BCD

For example, the decimal number "42" would be represented in BCD as "0100 0010". One of the main advantages of using BCD is that it allows for easy conversion between decimal and binary representations, which can simplify the design of digital circuits.

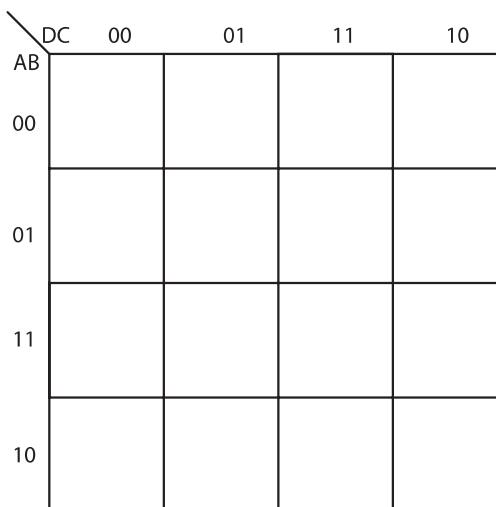

## PRELIMINARY PROCEDURE

1. Read the lab.

2. BCD invalid code detector:

- a. Determine the Prelab X output column in Table 5.2.

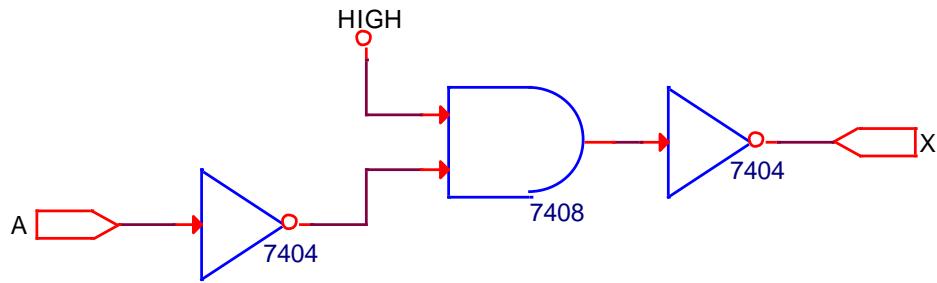

- b. Use Figure 5.1 (K-map) to determine the Boolean equation and its simplified expression.

- c. Use the simplified Boolean equation to draw the circuit in the box given in Figure 5.2.

- d. Number the pins of each gate in your circuit design.

3. BCD number divisible by three:

- a. Repeat steps a through e for Table 5.4, Figure 5.3, and Figure 5.4.

## PROCEDURE

---

### BCD INVALID CODE DETECTOR

1. Build the circuit designed in Figure 5.2 on a breadboard.

2. Complete the truth table in Table 5.2 to verify the output of your design. If the LED is on, X = 1.

| Input |   |   |   | Output   |                |                 |

|-------|---|---|---|----------|----------------|-----------------|

| A     | B | C | D | Prelab X | Experimental X | LED (On or Off) |

| 0     | 0 | 0 | 0 |          |                |                 |

| 0     | 0 | 0 | 1 |          |                |                 |

| 0     | 0 | 1 | 0 |          |                |                 |

| 0     | 0 | 1 | 1 |          |                |                 |

| 0     | 1 | 0 | 0 |          |                |                 |

| 0     | 1 | 0 | 1 |          |                |                 |

| 0     | 1 | 1 | 0 |          |                |                 |

| 0     | 1 | 1 | 1 |          |                |                 |

| 1     | 0 | 0 | 0 |          |                |                 |

| 1     | 0 | 0 | 1 |          |                |                 |

| 1     | 0 | 1 | 0 |          |                |                 |

| 1     | 0 | 1 | 1 |          |                |                 |

| 1     | 1 | 0 | 0 |          |                |                 |

| 1     | 1 | 0 | 1 |          |                |                 |

| 1     | 1 | 1 | 0 |          |                |                 |

| 1     | 1 | 1 | 1 |          |                |                 |

Table 5.2

Figure 5. 1: K-Map

Minimum sum-of-products reads from map:

$X = \underline{\hspace{10cm}}$

Factoring D from both terms gives:

$X = \underline{\hspace{10cm}}$

Draw the circuit with D factored out:

Figure 5. 2

| Problem Number | Problem                                                          | Effect |

|----------------|------------------------------------------------------------------|--------|

| 1              | Input D is open.                                                 |        |

| 2              | The ground to the AND gate is open.                              |        |

| 3              | A replace the $330\Omega$ resister with a $3.3k\Omega$ resister. |        |

| 4              | Insert the LED backwards.                                        |        |

| 5              | Input A is shorted to ground.                                    |        |

Table 5. 3

### BCD NUMBER DIVISIBLE BY THREE

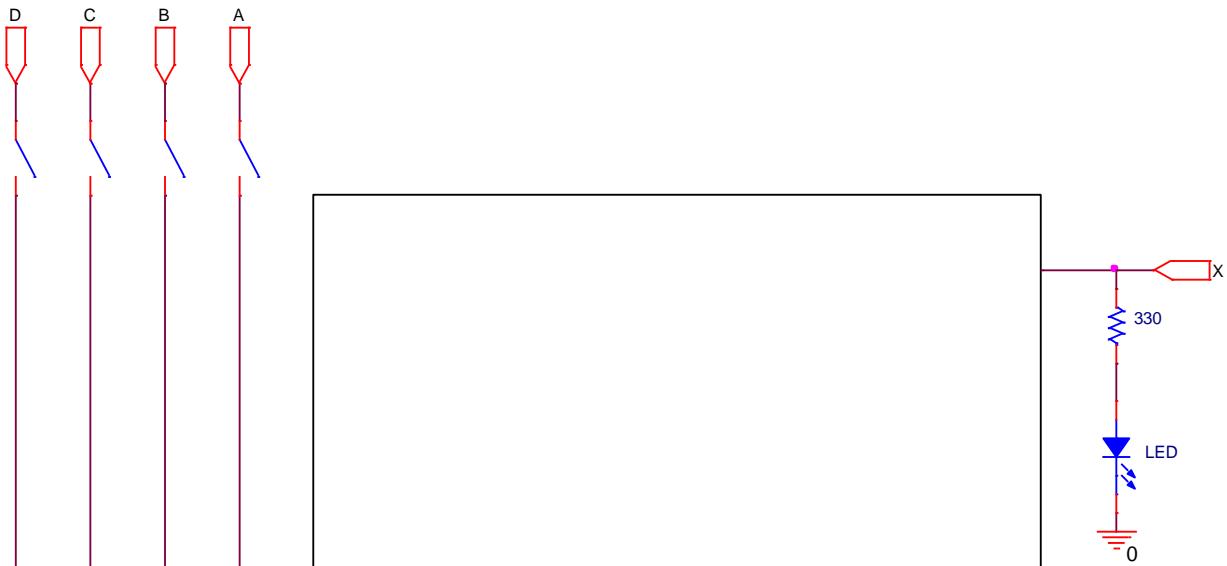

1. Build the circuit designed in Figure 5.4 on a breadboard.

2. Complete the truth table in Table 5.4 to verify the output of your design. If the LED is on, X = 1.

| Input |   |   |   | Output   |                |                 |

|-------|---|---|---|----------|----------------|-----------------|

| A     | B | C | D | Prelab X | Experimental X | LED (On or Off) |

| 0     | 0 | 0 | 0 |          |                |                 |

| 0     | 0 | 0 | 1 |          |                |                 |

| 0     | 0 | 1 | 0 |          |                |                 |

| 0     | 0 | 1 | 1 |          |                |                 |

| 0     | 1 | 0 | 0 |          |                |                 |

| 0     | 1 | 0 | 1 |          |                |                 |

| 0     | 1 | 1 | 0 |          |                |                 |

| 0     | 1 | 1 | 1 |          |                |                 |

| 1     | 0 | 0 | 0 |          |                |                 |

| 1     | 0 | 0 | 1 |          |                |                 |

| 1     | 0 | 1 | 0 |          |                |                 |

| 1     | 0 | 1 | 1 |          |                |                 |

| 1     | 1 | 0 | 0 |          |                |                 |

| 1     | 1 | 0 | 1 |          |                |                 |

| 1     | 1 | 1 | 0 |          |                |                 |

| 1     | 1 | 1 | 1 |          |                |                 |

Table 5.4

Figure 5.3: K-Map

Minimum sum-of-products reads from map:

X = \_\_\_\_\_

Draw the circuit:

Figure 5.4

## EVALUATION AND REVIEW QUESTIONS

1. Assume that the circuit in Figure 5.2 was constructed but doesn't work correctly. The output is correct for all inputs except DCBA - 1000 and 1001. Suggest at least two possible problems that could account for this and explain how you would isolate the exact problem.

2. Draw the equivalent circuit in Figure 5.2 using only NOR gates.

3. The A input was used in the truth table for the BCD invalid code detector (Table 5.2) but was not connected in the circuit in Figure 5.2. Explain why not.

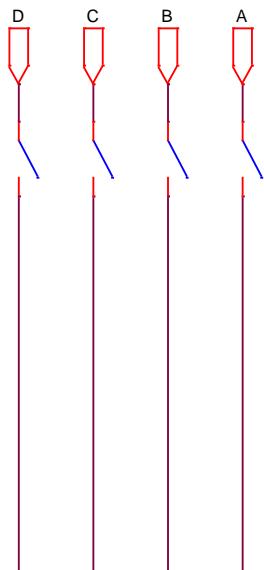

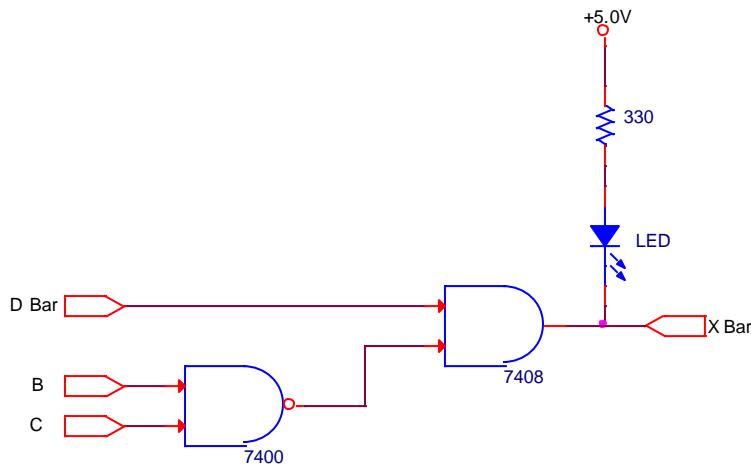

4. The circuit shown in Figure 5.6 has an output labeled "X Bar" =  $\bar{X}$ . Write the expression for  $\bar{X}$ ; then, using DeMorgan's theorem, find the expression for X.

Figure 5.5

5. Convert the SOP form of the expression for the invalid code detector (Step 2) into POS form.

6. Draw a circuit, using NAND gates, that implements the invalid code detector from the expression you found in Step 2.

## Half / Full Adder PSPICE Simulation

### OBJECTIVES

After completing this experiment, you will be able to

- Design and simulate a half adder.

- Design and simulate a fuller adder using two half adder modules.

- Build a full adder using two half adders and experimentally verify its functionality.

### MATERIALS NEEDED

- PSPICE

- One 7432 IC

- One 7486 IC

- One 7408 IC

### THEORY

#### HALF ADDER

A half adder is a type of digital logic circuit that is used to perform the addition of two binary digits. It has two inputs, called A and B, and two outputs, called sum and carry. The sum output is the XOR of the inputs, and the carry output is the AND of the inputs.

The truth table for a half adder:

| A | B | Carry | Sum |

|---|---|-------|-----|

| 0 | 0 | 0     | 0   |

| 0 | 1 | 0     | 1   |

| 1 | 0 | 0     | 1   |

| 1 | 1 | 1     | 0   |

Table 6. 1: Half Adder Truth Table

Half adders are often used in combination with other circuits to perform addition of larger binary numbers. For example, a full adder is a circuit that adds three binary digits and generates a carry output for addition of numbers larger than 2 bits.

#### FULL ADDER

A full adder is a digital circuit that performs the addition of two binary digits (bits) and a carry-in bit. The output of a full adder includes a sum bit and a carry-out bit. The sum bit is the result of the addition of the two input bits and the carry-in bit, while the carry-out bit is generated when the sum of the three input bits results in a value greater than 1 (in binary).

Full adders are commonly used in digital circuits to perform arithmetic operations, such as addition, subtraction, and multiplication. They are often used in combination with other digital circuits, such as multiplexers and flip-flops, to create more complex arithmetic logic units (ALUs) that can perform a wide range of arithmetic and logical operations.

The truth table for a full adder:

| A | B | C <sub>in</sub> | C <sub>out</sub> | Sum |

|---|---|-----------------|------------------|-----|

| 0 | 0 | 0               | 0                | 0   |

| 0 | 0 | 1               | 0                | 1   |

| 0 | 1 | 0               | 0                | 1   |

| 0 | 1 | 1               | 1                | 0   |

| 1 | 0 | 0               | 0                | 1   |

| 1 | 0 | 1               | 1                | 0   |

| 1 | 1 | 0               | 1                | 0   |

| 1 | 1 | 1               | 1                | 1   |

Table 6. 2: Full Adder Truth Table

in this truth table, A and B are the two input bits, Cin is the carry-in bit, Sum is the output sum bit, and Cout is the output carry-out bit.

## PRELIMINARY PROCEDURE

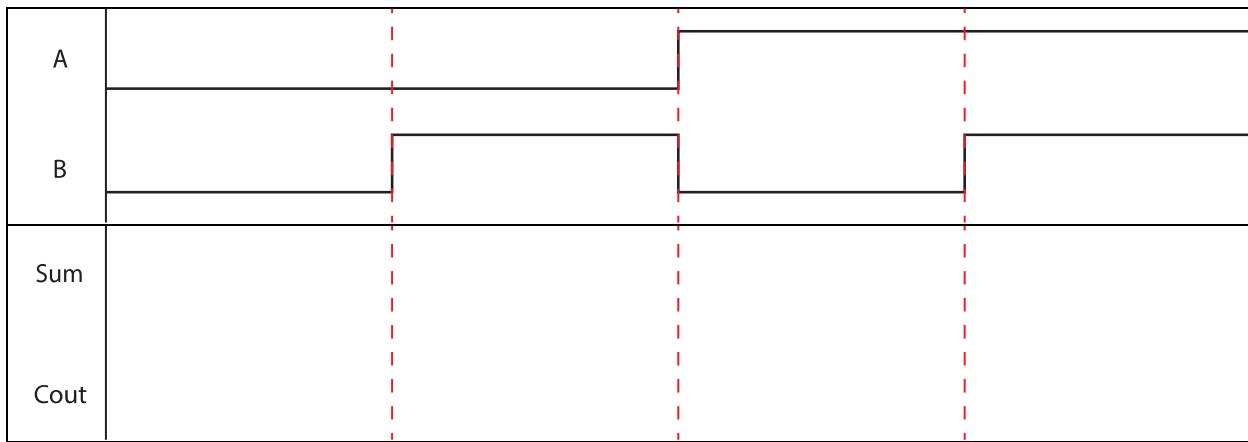

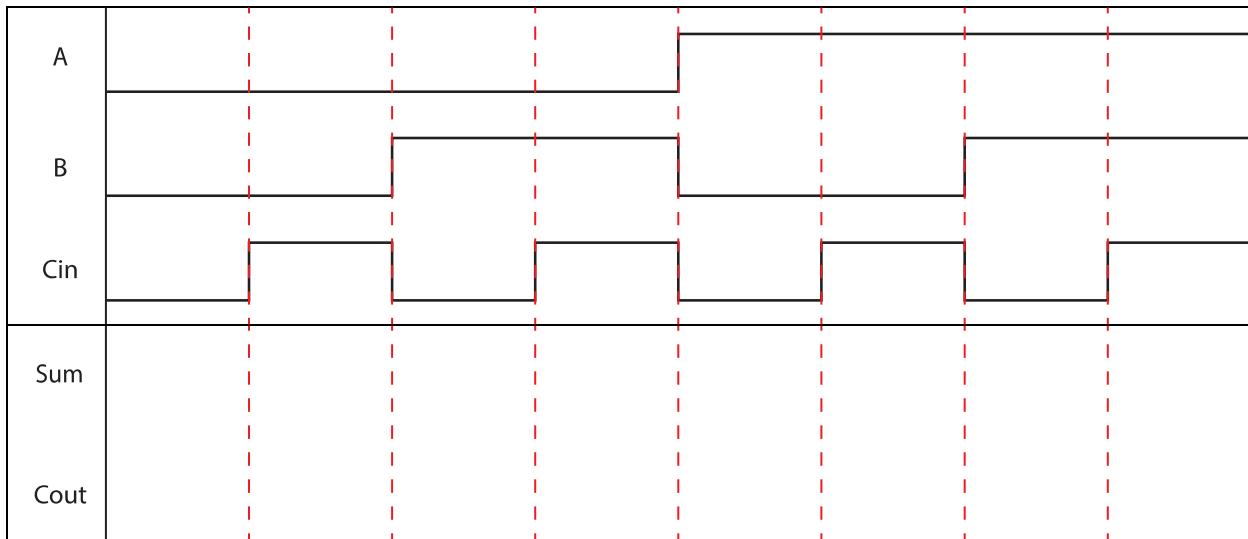

From the truth tables above, trace the output waveform for the half adder and full adder.

Figure 6. 1

Figure 6. 2

## PROCEDURE

---

### HALF ADDER IMPLEMENTATION

#### STARTING A NEW PROJECT

1. Create a new project by going to **File > New > New Project....**

2. In the New Project window, name your project and save it in a new folder.

3. In the Create PSPICE Project window, click **Create a blank project**, then press **OK**.

#### ADDING LIBRARIES

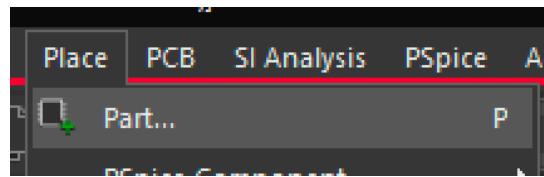

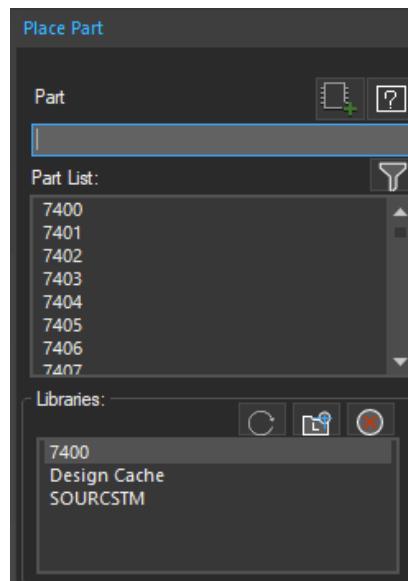

4. Press Place > Part or press P to bring up the parts library.

Figure 6. 3

5. In Place Part window, click the Add Library icon,  In the **Part** folder, open the library called 74LS, SOURCSTM.

Figure 6. 4

#### ADDING COMPONENTS TO SCHEMATIC

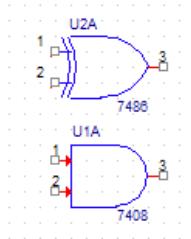

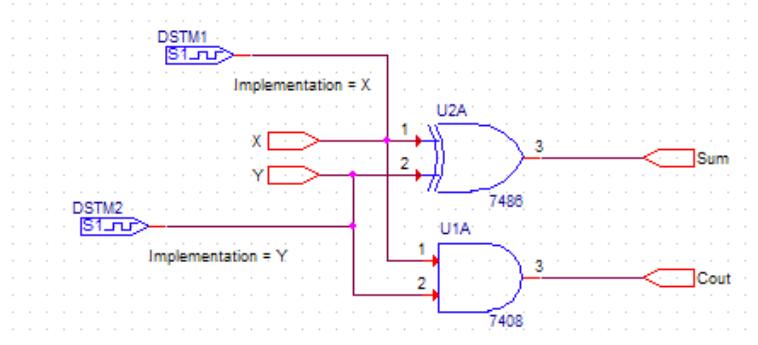

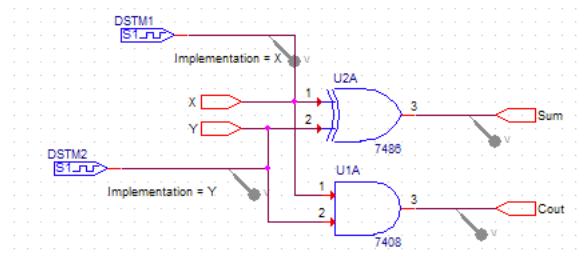

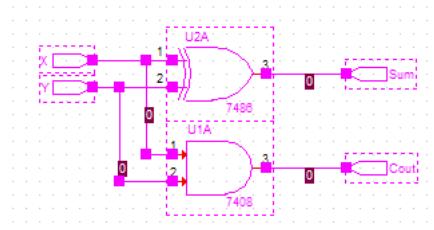

6. In the 7400 library, add the 7486 (XOR gate) and 7408 (AND gate) to the schematic.

Figure 6.5

7. Place two DigStim1 parts on your schematic (one for each input). Double click on the “Implementation” text and set the value to X and Y for each DigStim1.

8. Go to **Place > Hierarchical Port...** and place two PORTRIGHT-R ports to the left of the inputs of the XOR gate. Double click on the “PORTRIGHT-R” text and rename each port X and Y for each port.

9. Go to **Place > Hierarchical Port...** and place one PORTRIGHT-L port to the right of the output of the XOR gate. Double click on the “PORTLEFT-L” text and rename it SUM.

10. Go to **Place > Hierarchical Port...** and place one PORTRIGHT-L port to the right of the output of the AND gate. Double click on the “PORTLEFT-L” text and rename it OUT.

11. Press **W** for the wire tool and connect each component together with wires. So far you should have the following:

Figure 6.6

## CREATING A NEW SIMULATION PROFILE

12. Create a new simulation profile by pressing **PSpice > New Simulation Profile** or click the icon.

13. In the pop-up window type “halfadder-sim”. Press Create when done. Leave Inherit From as none.

14. A window called “Simulation Settings – lab1-sim” will pop-up. Set Run To Time to “1us”. This will make the simulation run for 1us.

15. Next, click on **Options > Gate Level Simulation > General** and set DIGINITSTATE to 0 under the Value column. Then press **Apply**, then **OK**.

## CREATING A SIMULATION STIMULI

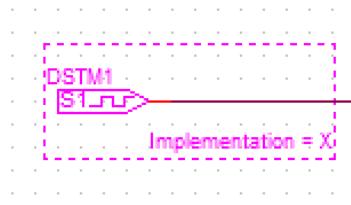

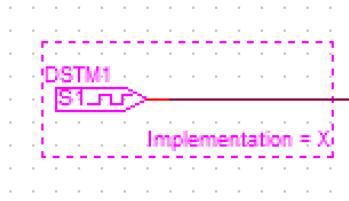

16. Click the DSTM1 symbol to select the part so that a purple dotted rectangle encloses the part.

Figure 6.7

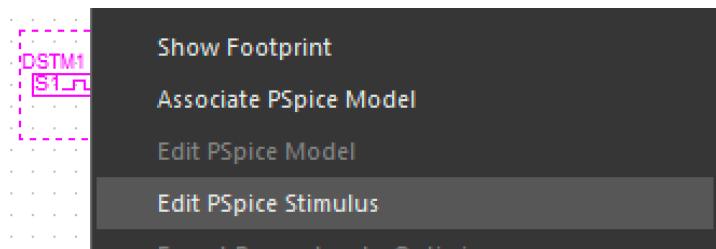

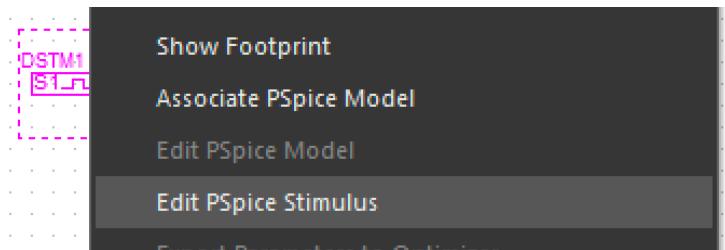

17. Right click on the DSTM1 symbol and click Edit PSpice Stimulus from the menu.

Figure 6.8

18. A New Stimulus window will pop up with "X" already in the Name text field. In the Digital section, select Signal, then press **OK**.

Figure 6.9

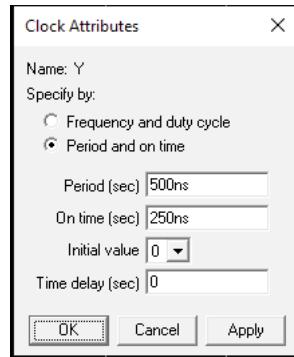

19. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 500ns and On time (sec) to 250ns. Press **Apply**, then **OK**.

Figure 6. 10

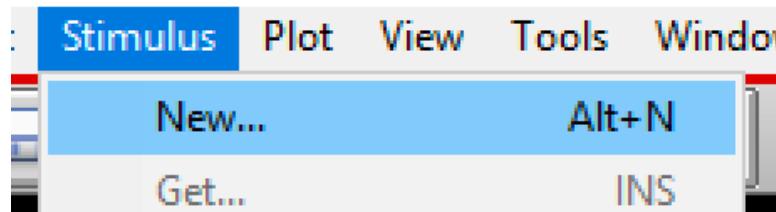

20. Set another stimulus for Y, press **Stimulus > New...**

Figure 6. 11

Figure 6. 12

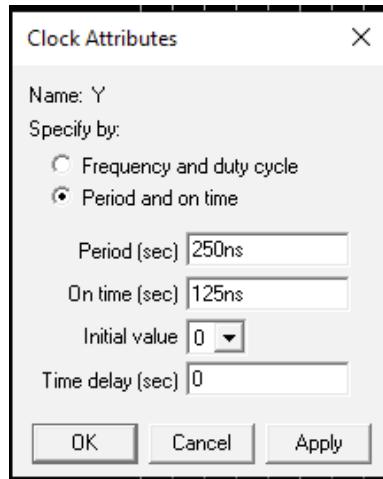

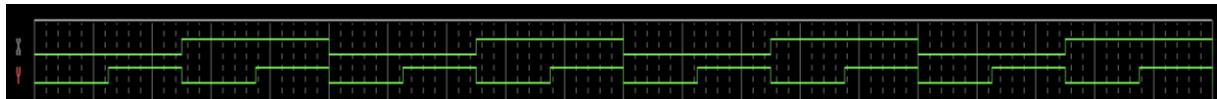

21. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 250ns and On time (sec) to 125ns. Press **Apply**, then **OK**.

22. Your Stimulus Editor should look like the following:

23. Press **Save** and press **Yes** to update schematic.

#### RUN SIMULATION

24. Place Voltage Level markers schematic by going to **PSPICE > Markers > Voltage Level** or press the  icon. The Voltage Level markers must be placed on the wires. Your schematic should look like the following:

Figure 6. 13

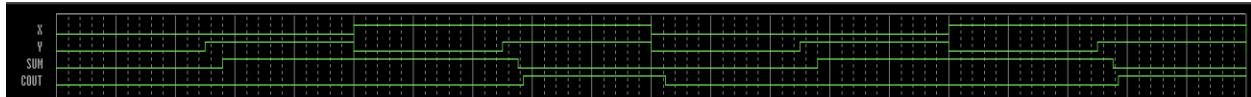

25. Press **PSpice > Run** or the  icon to run simulation. Running the simulation will cause the Allegro PSpice Simulator program to open which will contain a simulation of your schematic. It should look similar to the screenshot below:

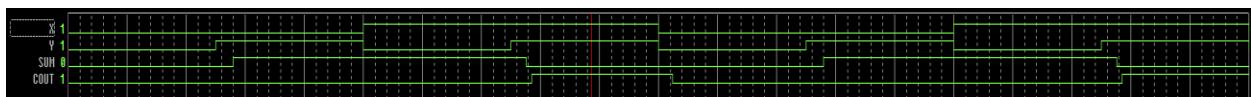

Figure 6.14

26. Press **Trace > Cursor > Display** or press  to enable the cursor. This will let you see the level of your signal. Once enabled, left click and on your simulation to see the levels of your signal. You can click hold and drag as well.

Figure 6.15

27. Compare your simulated results with your pre-lab.

## FULL ADDER IMPLEMENTATION

1. Open the halfadder project created in the previous section.

### STARTING A NEW PROJECT

2. Create a new project by going to **File > New > New Project....**

3. In the New Project window, name your project as fulladder and save it in a new folder.

4. In the Create PSPICE Project window, click **Create a blank project**, then press **OK**.

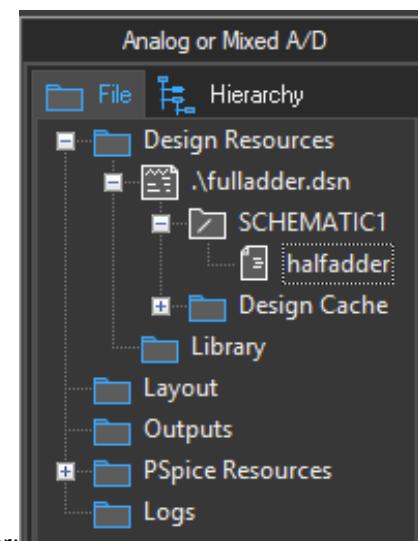

5. In the project file directory, right click PAGE1 and rename it as halfadder.

Figure 6.16

Figure 6.17

## ADDING LIBRARIES

- The necessary libraries should already be added to your library list from implementing the halfadder. If not, refer to step 4 in the from the previous section.

#### COPYING HALF ADDER TO SCHEMATIC

- In the halfadder project, open the half adder schematic. Then left click drag over the halfadder until the entire circuit is selected. All components will be highlighted in purple:

Figure 6. 18

- Go to **Edit > Copy** or press **Ctrl+C** to copy the halfadder circuit.

- Paste the halfadder circuit on to the new schematic named halfadder.

#### FULL ADDER SCHEMATIC

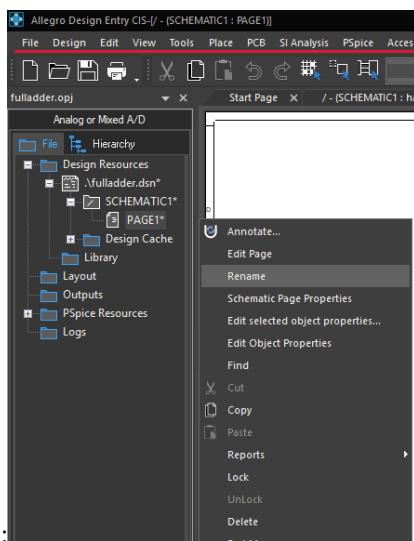

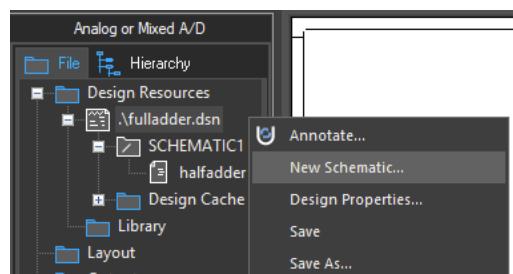

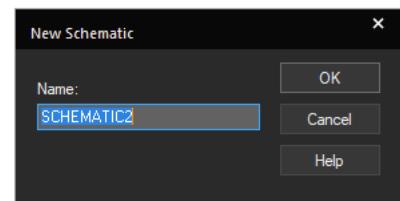

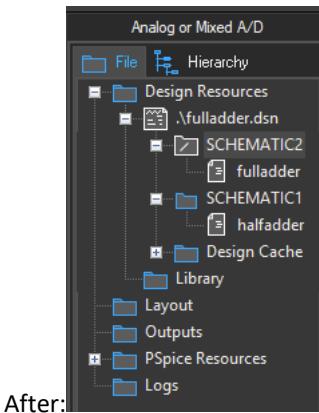

- In the project file directory, right click **fulladder.dsn** and click on **New Schematic...**. Leave the schematic name as the default, **SCHEMATIC2**.

Figure 6. 19

Figure 6. 20

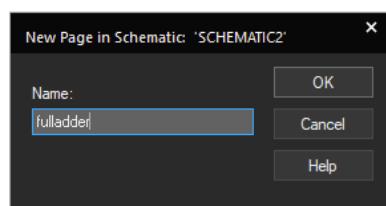

- Right click the **SCHEMATIC2** folder created in the project directory and click **New Page**. Rename the new page as **fulladder**.

Figure 6. 21

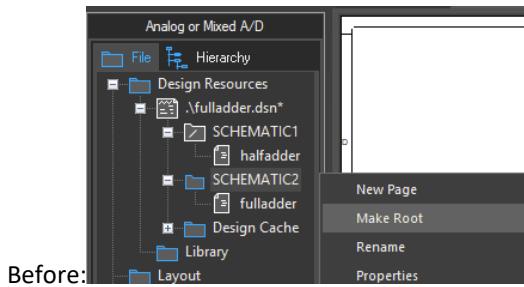

12. Set SCHEMATIC2 as root folder. Right click SCHEMATIC2 and click **Make Root**. This will move SCHEMATIC2 to the top.

Figure 6. 22

Figure 6. 23

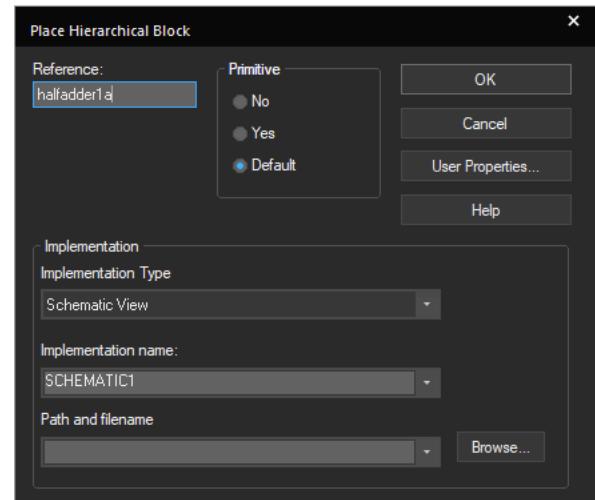

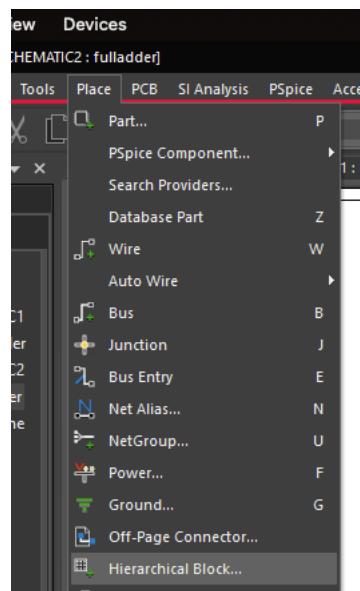

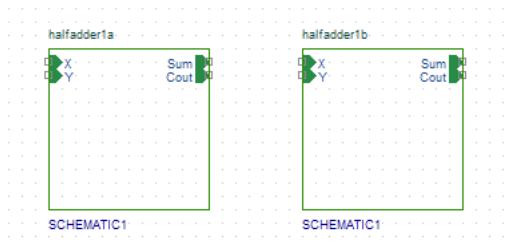

13. Go to **Place > Hierarchical Block....** In the Place Hierarchical Block window, set Reference to **halfadder1a**, Implementation Type to **Schematic View**, and Implementation name to **SCHEMATIC1**. Then press **OK**.

Figure 6.

Figure 6. 24

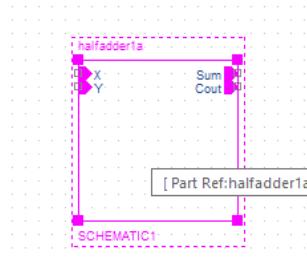

14. Left-click and drag to form a hierarchical box as shown below:

Figure 6.25

15. Repeat step 12 and 13 to add another halfadder hierarchical block, however, name this one **halfadder1b**.

Figure 6.26

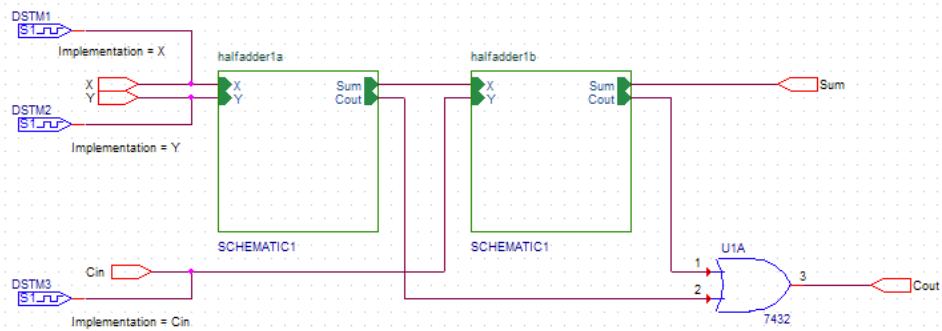

16. Add the 7432 OR gate (7400 library), DigStim1 (X, Y, Cin), PORTRIGHT-R (X, Y, Cin), and wires to the schematic. Wire your circuit together as shown below:

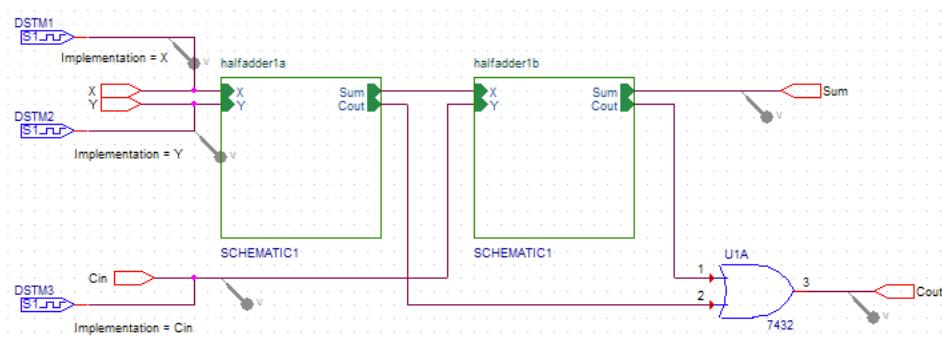

Figure 6.27

## CREATING A NEW SIMULATION PROFILE

17. Create a new simulation profile by pressing **PSpice > New Simulation Profile** or click the icon.

18. In the pop-up window type “fulladder-sim”. Press Create when done. Leave Inherit From as none.

19. A window called “Simulation Settings – lab1-sim” will pop-up. Set Run To Time to “1us”. This will make the simulation run for 1us.

20. Next, click on **Options > Gate Level Simulation > General** and set DIGINITSTATE to 0 under the Value column. Then press **Apply**, then **OK**.

## CREATING A SIMULATION STIMULI

21. Click the DSTM1 symbol to select the part so that a purple dotted rectangle encloses the part.

Figure 6.28

22. Right click on the DSTM1 symbol and click Edit PSpice Stimulus from the menu.

Figure 6.29

23. A New Stimulus window will pop up with "X" already in the Name text field. In the Digital section, select Signal, then press **OK**.

Figure 6.30

24. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 1000ns and On time

(sec) to 500ns. Press **Apply**, then **OK**.

Figure 6. 31

25. Set another stimulus for Y, press **Stimulus > New...**

Figure 6. 32

26. Set Name to Y and Digital to **Clock**.

Figure 6. 33

27. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 500ns and On time (sec) to 250ns. Press **Apply**, then **OK**.

Figure 6. 34

28. Set another stimulus for Cin, press **Stimulus > New....**

Figure 6. 35

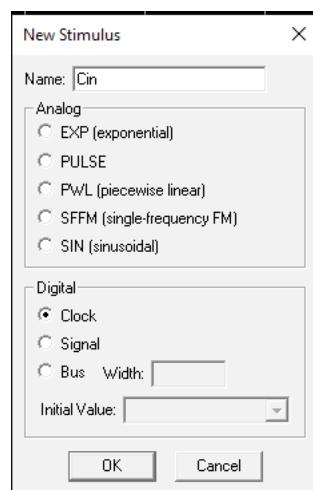

29. Set Name to **Cin** and Digital to **Clock**.

Figure 6. 36

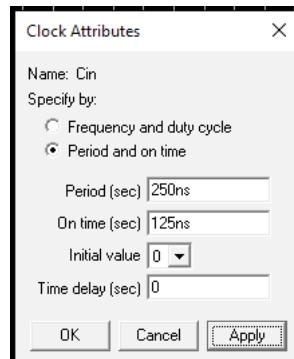

30. In the Clock Attributes window, set Specify by to Period and on time. Set Period (sec) to 250ns and On time (sec) to 125ns. Press **Apply**, then **OK**.

(sec) to 125ns. Press **Apply**, then **OK**.

Figure 6. 37

31. Your Stimulus Editor should look like the following:

Figure 6. 38

32. Press **Save** and press **Yes** to update schematic.

#### RUN SIMULATION

33. Place Voltage Level markers schematic by going to **PSpice > Markers > Voltage Level** or press the  icon. The Voltage Level markers must be placed on the wires. Your schematic should look like the following:

Figure 6. 39

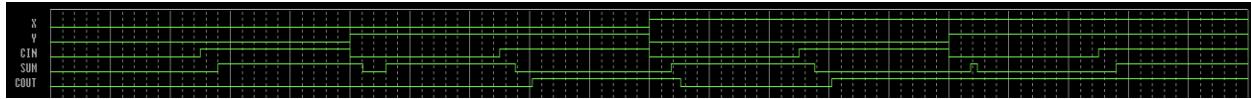

34. Press **PSpice > Run** or the  icon to run simulation. Running the simulation will cause the Allegro PSpice Simulator program to open which will contain a simulation of your schematic. It should look similar to the screenshot below:

Figure 6. 40

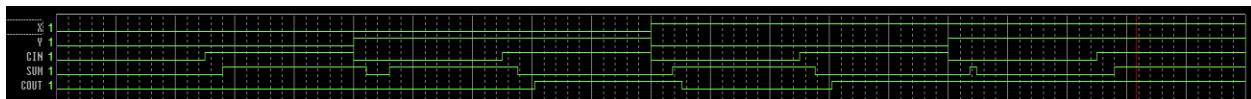

35. Press **Trace > Cursor > Display** or press  to enable the cursor. This will let you see the level of your signal. Once enabled, left click and on your simulation to see the levels of your signal. You can click hold and drag as well.

Figure 6. 41

36. Compare your simulated results with your pre-lab.

## BREADBOARD

1. Draw the gate level schematic of the full adder designed in part A, build it on a breadboard, and verify its functionality.

2. Record the output in Table 6.3 and compare your results with Table 6.2.

| Input |   |          | Output    |     |

|-------|---|----------|-----------|-----|

| A     | B | $C_{in}$ | $C_{out}$ | Sum |

| 0     | 0 | 0        |           |     |

| 0     | 0 | 1        |           |     |

| 0     | 1 | 0        |           |     |

| 0     | 1 | 1        |           |     |

| 1     | 0 | 0        |           |     |

| 1     | 0 | 1        |           |     |

| 1     | 1 | 0        |           |     |

| 1     | 1 | 1        |           |     |

Table 6. 3: Full adder truth table

## 2's Complement Adder / Subtractor Circuit

### OBJECTIVES

After completing this experiment, you will be able to:

- Design, draw, construct, test, and demonstrate a 2s complement adder/subtractor system using only 7483 and 7486 ICs

### MATERIALS NEEDED

- 7483 4-bit adder IC

- 7486 quad two-input XOR gate IC

- 4 LEDs

- 4  $330\Omega$  resistors

### THEORY

#### ADDER / SUBTRACTOR CIRCUIT

A 4-bit adder/subtractor circuit can be constructed using a 7483 4-bit binary full adder and a 7486 XOR gate IC. The 7483 IC performs the addition, while the 7486 IC is used to handle the subtraction operation. The 7483 IC has two inputs for each of the four bits ( $A_0, A_1, A_2, A_3$ ) and ( $B_0, B_1, B_2, B_3$ ), and the carry-in ( $C_{in}$ ) and carry-out ( $C_{out}$ ) lines.

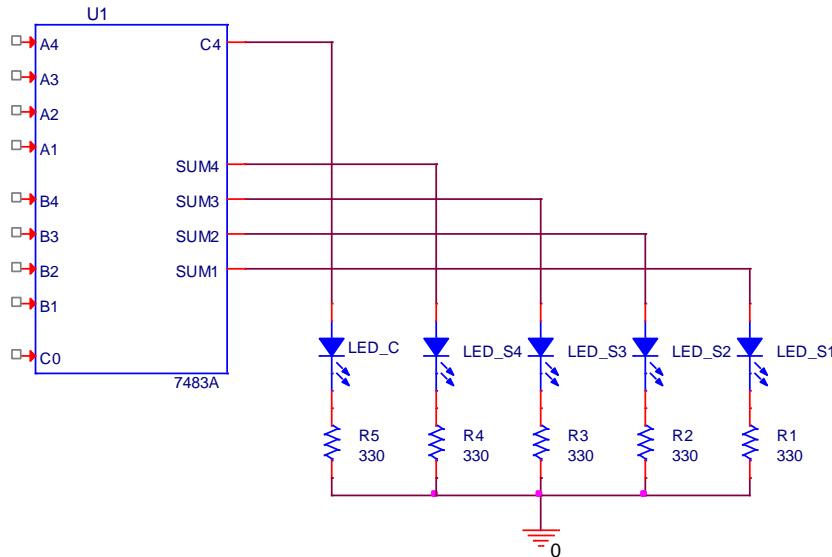

Figure 7.1

### 2'S COMPLEMENT

#### CONVERTING BETWEEN UNSIGNED AND SIGNED 2'S COMPLEMENT

In computing, the two's complement is a method used to represent signed integers. It allows both positive and negative numbers to be stored and manipulated using the same binary arithmetic operations. In this representation, the most significant bit (MSB) is used to represent the sign of the number, where 0 indicates a positive number and 1 indicates a negative number.

To obtain the two's complement representation of a negative number, you follow these steps:

#### EXAMPLE 1: UNSIGNED TO 2'S COMPLEMENT

Let's find the two's complement representation of the decimal number -20 using 8-bit binary representation:

1. Write the digit as a positive unsigned binary number:

$$+20 = 00010100$$

- Starting from the right-hand side and moving to the left, copy all the bits including the first '1' reached:

Giving us: 00010**100** → **100**

- Take the complement of the remaining bits:

Giving us: **00010** → **11101**

Therefore, the two's complement representation of -20 in 8-bit binary is 11101100.

#### EXAMPLE 2: 2'S COMPLEMENT TO UNSIGNED

Now let's convert back from the two's complement representation to the decimal representation:

- Starting from the right-hand side and moving to the left, copy all the bits including the first '1' reached:

Giving us: 11101**100** → **100**

- Take the complement of the remaining bits:

Giving us: **11101** → **00010**

- Finally, interpret the result as a positive binary number:

$$+20 = 00010100$$

In this way, the two's complement representation allows us to perform arithmetic operations on signed integers using the standard binary arithmetic operations.

#### ADDITION AND SUBTRACTION WITH 2'S COMPLEMENT

##### EXAMPLE 3: ADDITION

Let's add two numbers, 3 and -2, represented in 4-bit two's complement.

- Represent the numbers in 4-bit binary form:

$$3 = 0011 \text{ (4-bit binary)}$$

$$-2 = 2\text{'s complement of 2 (which is 0010)} = 1110 \text{ (4-bit binary)}$$

- Add the binary numbers as if they were unsigned binary:

$$\begin{array}{r} 0011 \text{ (3)} \\ + 1110 \text{ (-2)} \\ \hline 10001 \text{ (Carry-out)} \end{array}$$

- Discard any overflow and keep the lower 4 bits of the result:

$$0001 \text{ (discard the carry-out)}$$

4. Interpret the result as a signed decimal number:

0001 (4-bit binary) = 1 (decimal)

Therefore, the result of adding 3 and -2 using two's complement representation is 1.

#### EXAMPLE 4: SUBTRACTION

Let's subtract two numbers, 5 and 3, represented in 4-bit two's complement.

1. Represent the numbers in 4-bit binary form:

5 = 0101 (4-bit binary)

3 = 0011 (4-bit binary)

2. Find the two's complement of the number to be subtracted (3):

-3 (decimal) = -2's complement of 3 (which is 0011) = 1101 (4-bit binary)

3. Add the binary numbers as if they were unsigned binary:

$$\begin{array}{r} 0101 \text{ (5)} \\ + 1101 \text{ (-3)} \\ \hline 10010 \text{ (Carry-out)} \end{array}$$

4. Discard any overflow and keep the lower 4 bits of the result:

0010 (discard the carry-out)

Step 5: Interpret the result as a signed decimal number:

0010 (4-bit binary) = 2 (decimal)

Therefore, the result of subtracting 3 from 5 using two's complement representation is 2.

In summary, two's complement allows us to perform addition and subtraction of signed integers using the same binary arithmetic operations as for unsigned integers. It simplifies the calculations and representation of negative numbers in computer systems.

#### PRELIMINARY PROCEDURE

---

1. Read the lab.

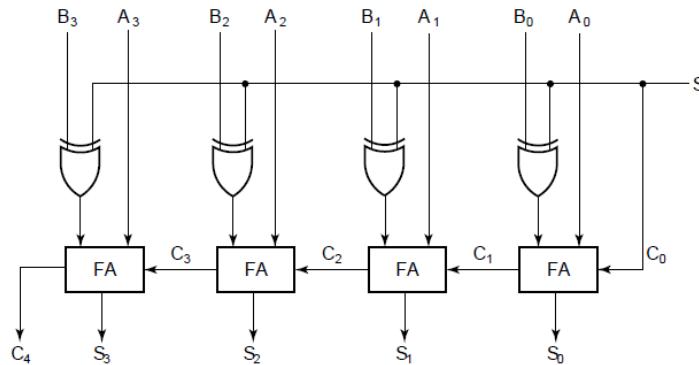

2. Design the 2s complement adder/subtractor system shown in Figure 7.2. Use a 7486 IC for the four XOR gates. Use a single 7483 adder IC for the four full adders (FAs).

3. Number the pins on your design using the datasheets.

#### PROCEDURE

---

1. Circuit design:

Figure 7.2

2. Find the sum of the following 4-bit 2's compliment numbers:

| Inputs                   |                 | Outputs |                                                                  |

|--------------------------|-----------------|---------|------------------------------------------------------------------|

| $A + B = S_{\text{Sum}}$ |                 | Sum     | LEDs, Sum                                                        |

| $4 + 3 = 7$              | $0100 + 0011 =$ | 0111    | OFF <sub>4</sub> ON <sub>3</sub> ON <sub>2</sub> ON <sub>1</sub> |

| $-1 + -1 = -2$           | $1111 + 1110 =$ |         |                                                                  |

| $1 + -2 = -2$            | $0001 + 1101 =$ |         |                                                                  |

| $5 + -4 = 1$             | $0101 + 1100 =$ |         |                                                                  |

Table 7.1

3. Find the difference of the following 4-bit 2's complement numbers. The '+' is not a typo:

| Inputs                    |                 | Outputs    |                                                                    |

|---------------------------|-----------------|------------|--------------------------------------------------------------------|

| $A - B = D_{\text{Diff}}$ |                 | Difference | LEDs, Diff                                                         |

| $7 - 3 = 4$               | $0111 + 1101 =$ | 0100       | OFF <sub>4</sub> ON <sub>3</sub> OFF <sub>2</sub> OFF <sub>1</sub> |

| $-8 - 3 = -5$             | $1000 + 0011 =$ |            |                                                                    |

| $3 - -3 = 6$              | $0011 + 0011 =$ |            |                                                                    |

| $-4 - 2 = -6$             | $1100 + 1110 =$ |            |                                                                    |

Table 7.2

### EVALUATION AND REVIEW QUESTIONS

1. Draw an 8-bit 2's Complement Adder/Subtractor circuit using two 7483 4-bit adder ICs and eight 7486 quad two-input XOR gate ICs. Build can test your circuit if you have the parts and time during lab.

# Multiplexers

## OBJECTIVES

After completing this experiment, you will be able to:

- Use a multiplexer to construct a unsigned comparator, signed comparator, and a parity generator and verify it's functionality.

- Use an N-input multiplexer to implement a truth table containing  $2N$  inputs.

- Troubleshoot a simulated failure in a test circuit.

## MATERIALS NEEDED

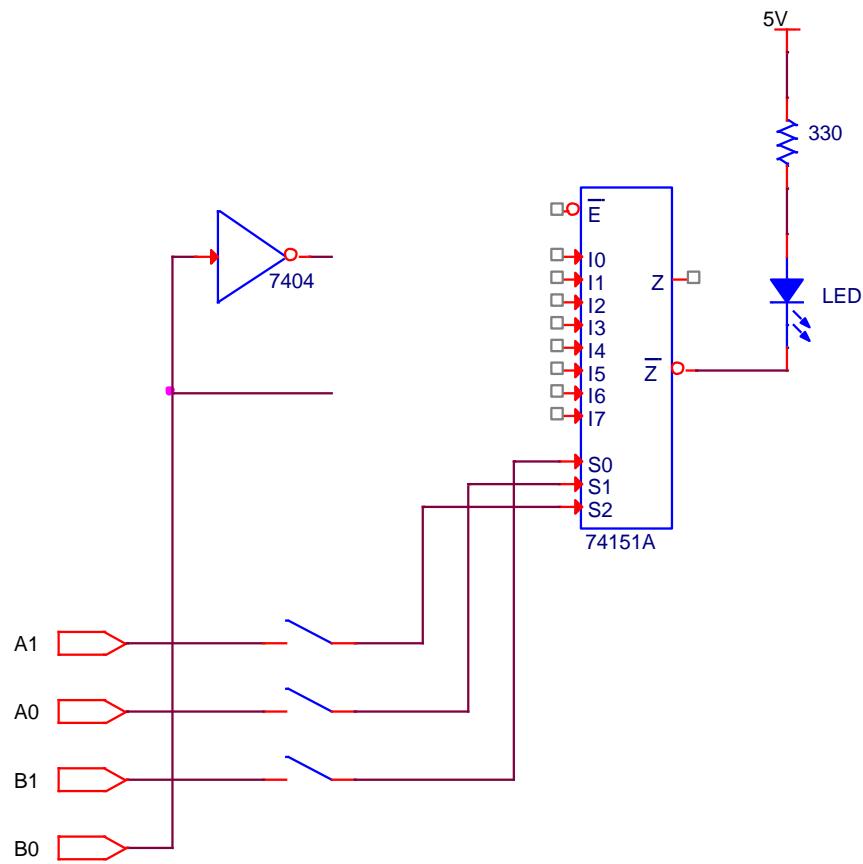

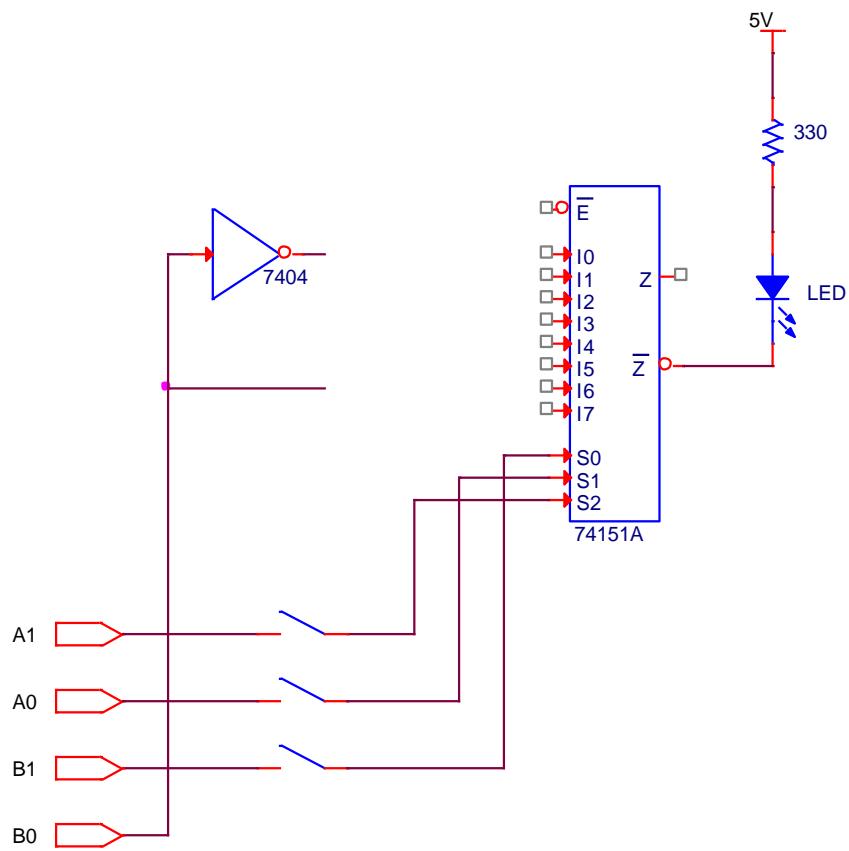

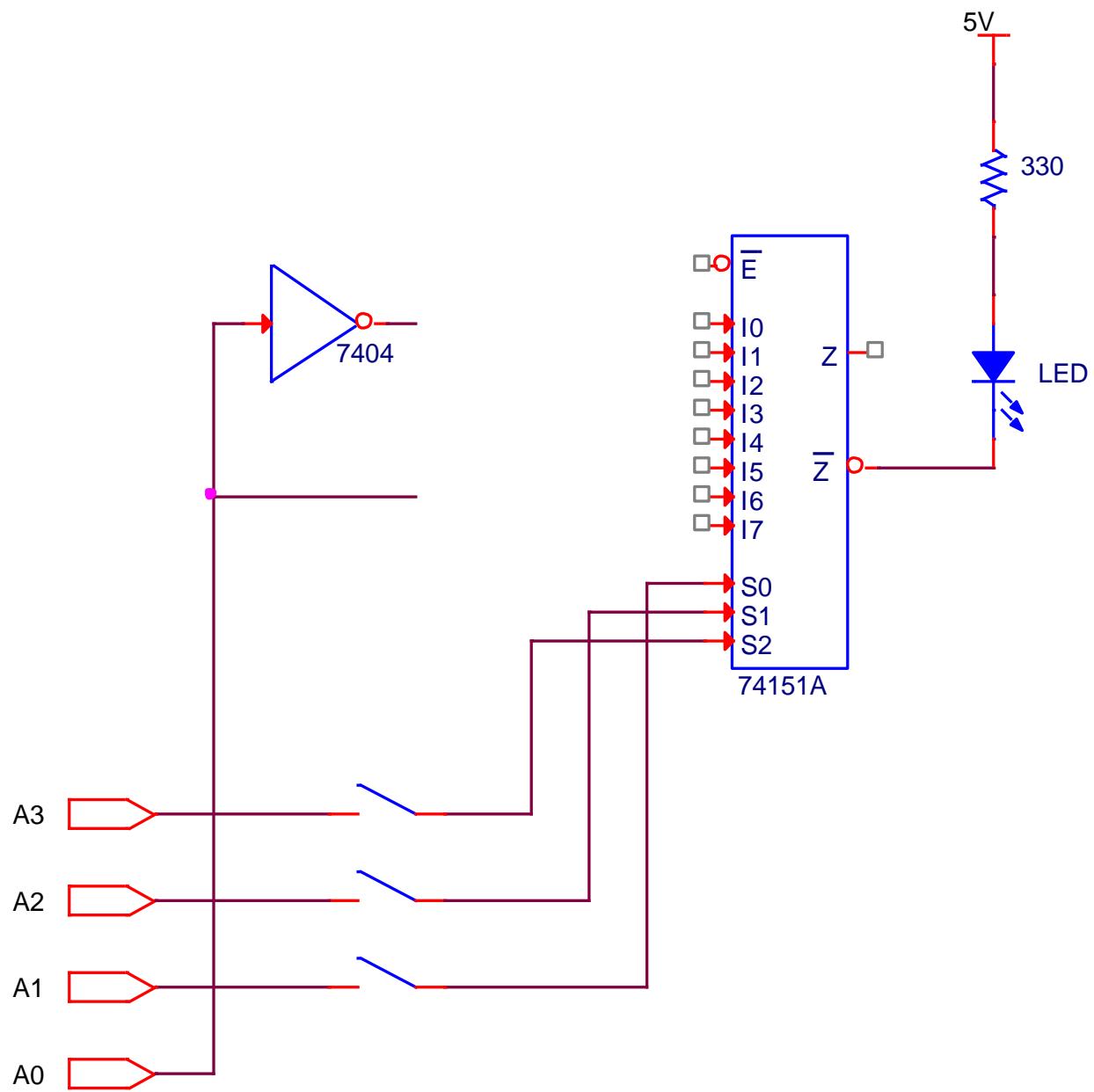

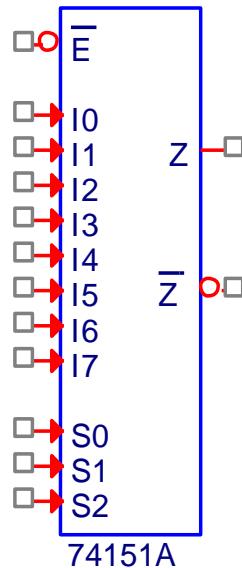

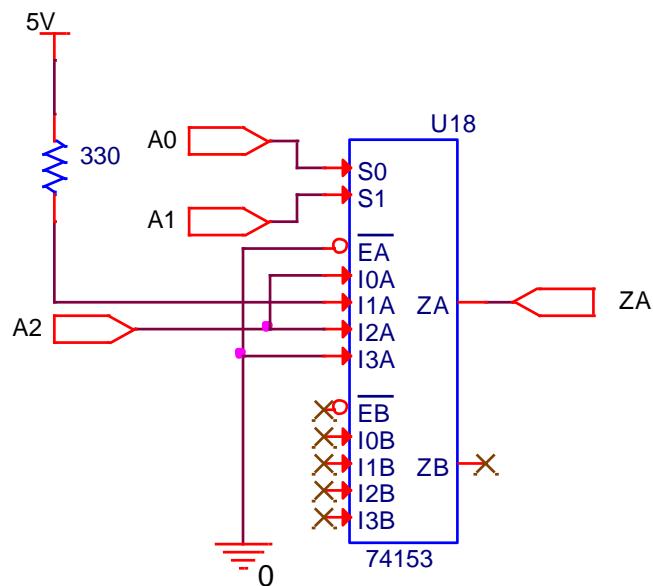

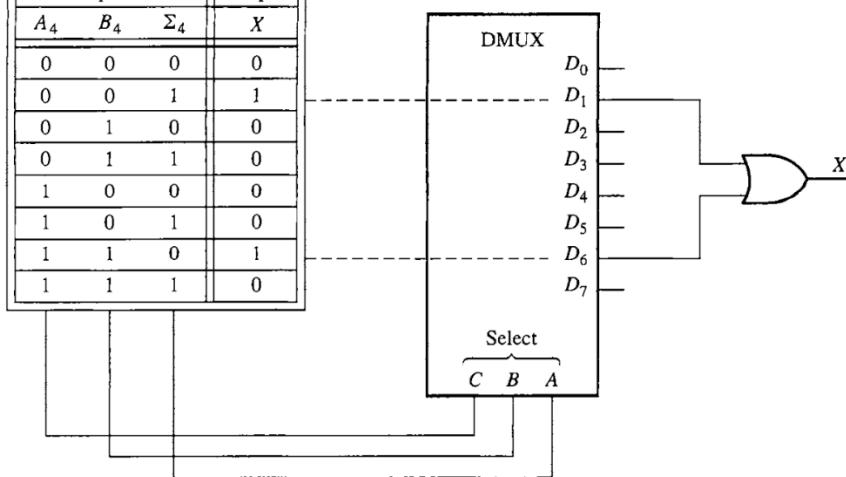

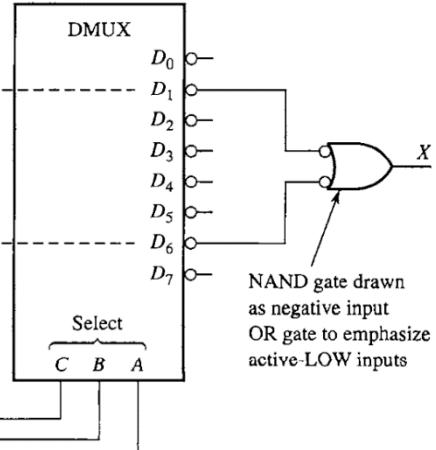

- 74151A data selector/multiplexer

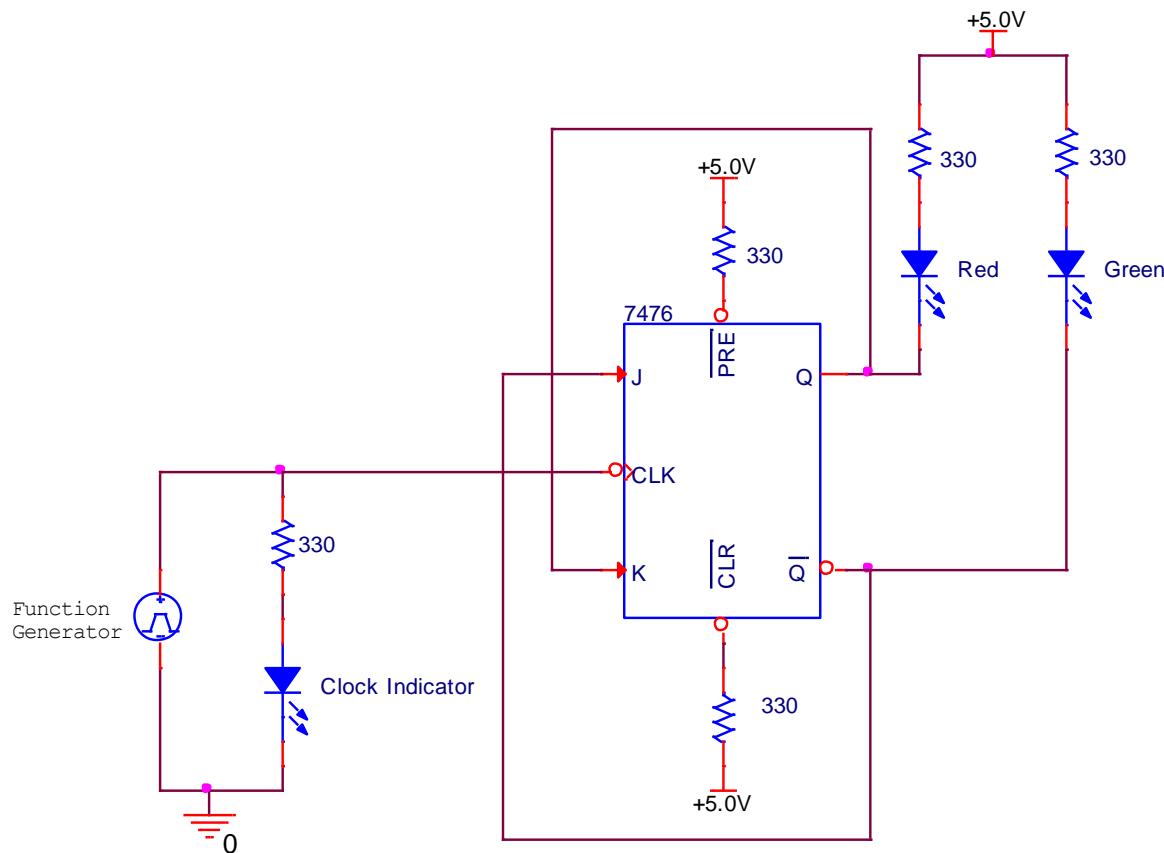

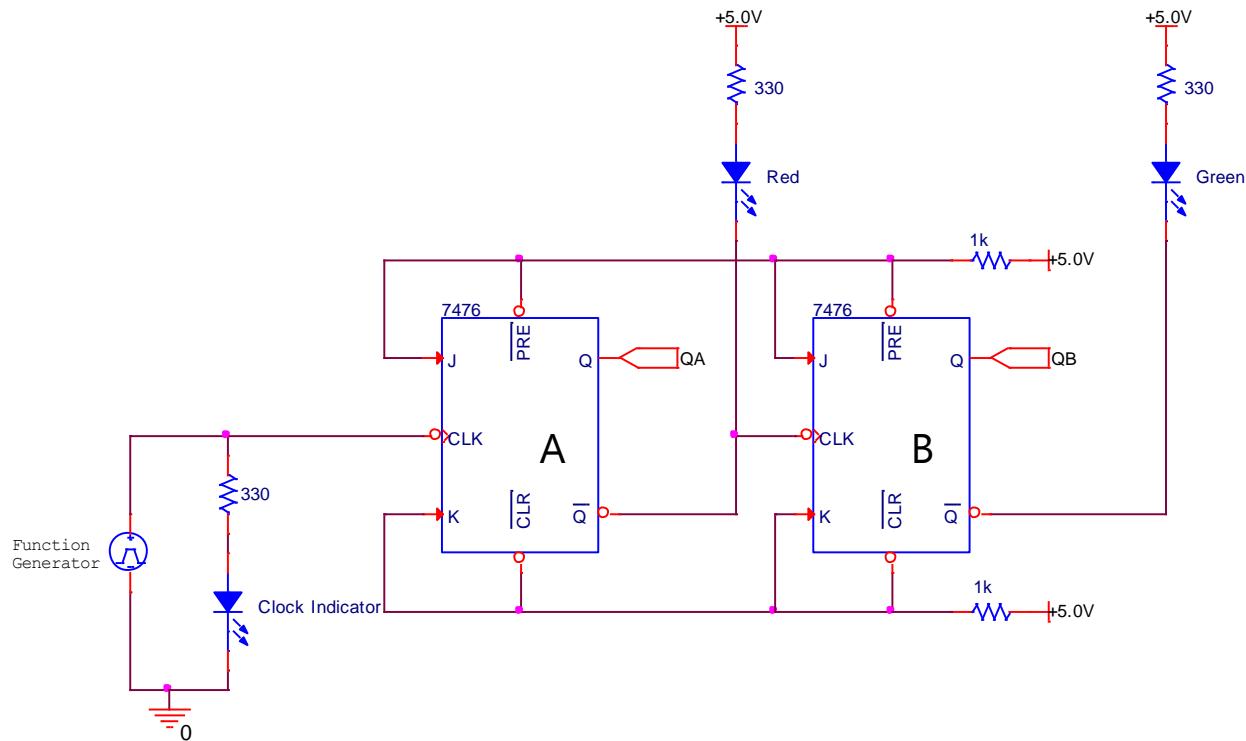

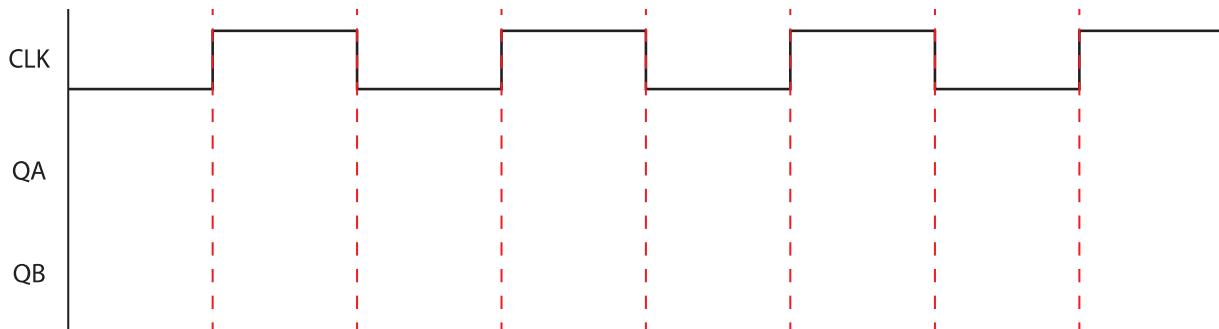

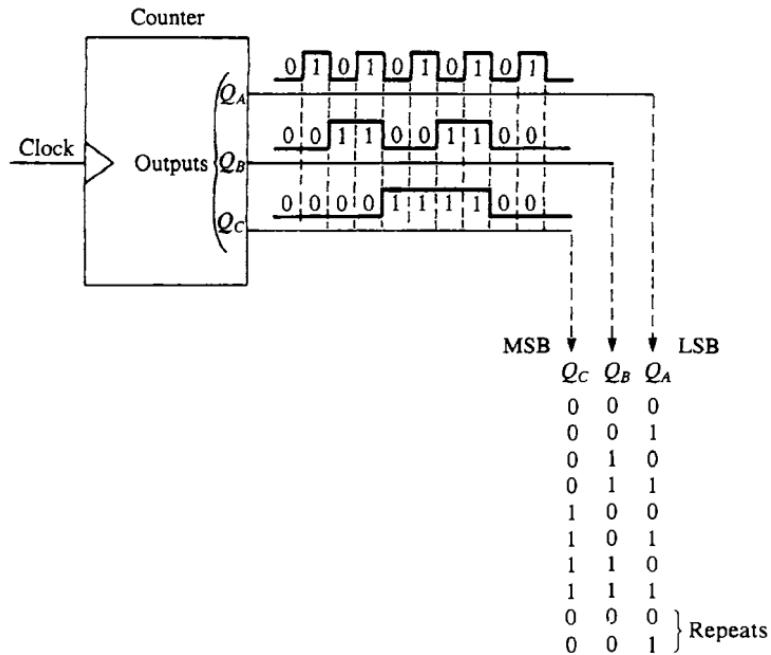

- 7404 hex inverter